# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# R8C/32D Group

Hardware Manual Renesas MCU R8C Family / R8C/3x Series

All information contained in this material, including products and product specifications at the time of publication of this material, is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

www.renesas.com

### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

You should not use the products or the technology described in this document for the purpose of military

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

### General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

#### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

— The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the second content is applied to the external reset pin.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

### 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

### 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

— When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

### 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

# How to Use This Manual

### 1. Purpose and Target Readers

This manual is designed to provide the user with an understanding of the hardware functions and electrical characteristics of the MCU. It is intended for users designing application systems incorporating the MCU. A basic knowledge of electric circuits, logical circuits, and MCUs is necessary in order to use this manual.

The manual comprises an overview of the product; descriptions of the CPU, system control functions, peripheral functions, and electrical characteristics; and usage notes.

Particular attention should be paid to the precautionary notes when using the manual. These notes occur within the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the locations of revisions and additions. It does not list all revisions. Refer to the text of the manual for details.

The following documents apply to the R8C/32D Group. Make sure to refer to the latest versions of these documents. The newest versions of the documents listed may be obtained from the Renesas Technology Web site.

| Document Type    | Description                                         | Document Title      | Document No.  |

|------------------|-----------------------------------------------------|---------------------|---------------|

| Shortsheet       | Hardware overview                                   | R8C/32D Group       | REJ03B0288    |

|                  |                                                     | Shortsheet          |               |

| Hardware manual  | Hardware specifications (pin assignments,           | R8C/32D Group       | This hardware |

|                  | memory maps, peripheral function                    | Hardware Manual     | manual        |

|                  | specifications, electrical characteristics, timing  |                     |               |

|                  | charts) and operation description                   |                     |               |

|                  | Note: Refer to the application notes for details on |                     |               |

|                  | using peripheral functions.                         |                     |               |

| Software manual  | Description of CPU instruction set                  | R8C/Tiny Series     | REJ09B0001    |

|                  |                                                     | Software Manual     |               |

| Application note | Information on using peripheral functions and       | Available from Rene | esas          |

|                  | application examples                                | Technology Web sit  | e.            |

|                  | Sample programs                                     |                     |               |

|                  | Information on writing programs in assembly         |                     |               |

|                  | language and C                                      |                     |               |

| Renesas          | Product specifications, updates on documents,       |                     |               |

| technical update | etc.                                                |                     |               |

## 2. Notation of Numbers and Symbols

The notation conventions for register names, bit names, numbers, and symbols used in this manual are described below.

### (1) Register Names, Bit Names, and Pin Names

Registers, bits, and pins are referred to in the text by symbols. The symbol is accompanied by the word "register," "bit," or "pin" to distinguish the three categories.

Examples the PM03 bit in the PM0 register

P3\_5 pin, VCC pin

### (2) Notation of Numbers

The indication "b" is appended to numeric values given in binary format. However, nothing is appended to the values of single bits. The indication "h" is appended to numeric values given in hexadecimal format. Nothing is appended to numeric values given in decimal format.

Examples Binary: 11b

Hexadecimal: EFA0h Decimal: 1234

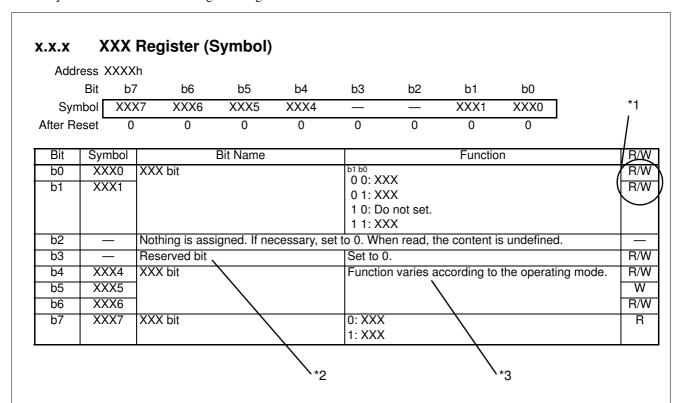

### 3. Register Notation

The symbols and terms used in register diagrams are described below.

\*1

R/W: Read and write.

R: Read only.

W: Write only.

-: Nothing is assigned.

\*2

· Reserved bit

Reserved bit. Set to specified value.

\*3

• Nothing is assigned.

Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.

• Do not set to a value.

Operation is not guaranteed when a value is set.

• Function varies according to the operating mode.

The function of the bit varies with the peripheral function mode. Refer to the register diagram for information on the individual modes.

# 4. List of Abbreviations and Acronyms

| Abbreviation | Full Form                                    |

|--------------|----------------------------------------------|

| ACIA         | Asynchronous Communication Interface Adapter |

| bps          | bits per second                              |

| CRC          | Cyclic Redundancy Check                      |

| DMA          | Direct Memory Access                         |

| DMAC         | Direct Memory Access Controller              |

| GSM          | Global System for Mobile Communications      |

| Hi-Z         | High Impedance                               |

| IEBus        | Inter Equipment Bus                          |

| I/O          | Input/Output                                 |

| IrDA         | Infrared Data Association                    |

| LSB          | Least Significant Bit                        |

| MSB          | Most Significant Bit                         |

| NC           | Non-Connection                               |

| PLL          | Phase Locked Loop                            |

| PWM          | Pulse Width Modulation                       |

| SIM          | Subscriber Identity Module                   |

| UART         | Universal Asynchronous Receiver/Transmitter  |

| VCO          | Voltage Controlled Oscillator                |

# **Table of Contents**

| SFR Pag    | e Reference                                                | B - 1    |

|------------|------------------------------------------------------------|----------|

| 1. Ov      | verview                                                    | 1        |

| 1.1        | Features                                                   | 1        |

| 1.1.1      | Applications                                               | 1        |

| 1.1.2      | Specifications                                             | 2        |

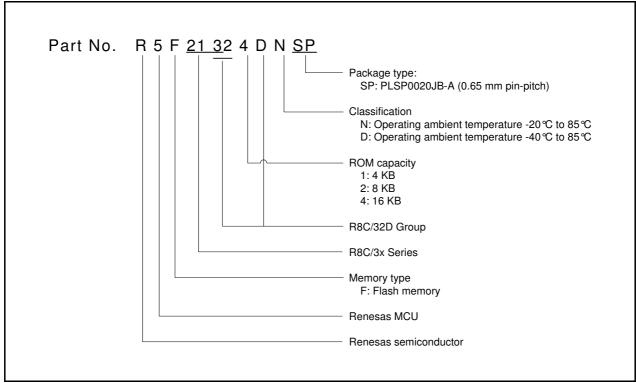

| 1.2        | Product List                                               | 4        |

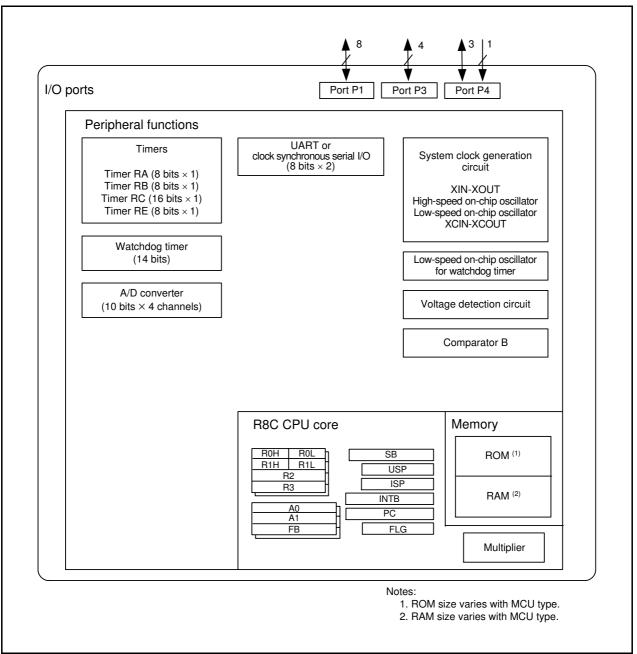

| 1.3        | Block Diagram                                              | 5        |

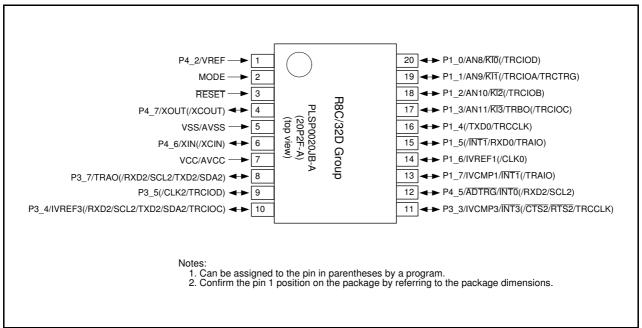

| 1.4        | Pin Assignment                                             | 6        |

| 1.5        | Pin Functions                                              | 8        |

| 2. Ce      | entral Processing Unit (CPU)                               | 9        |

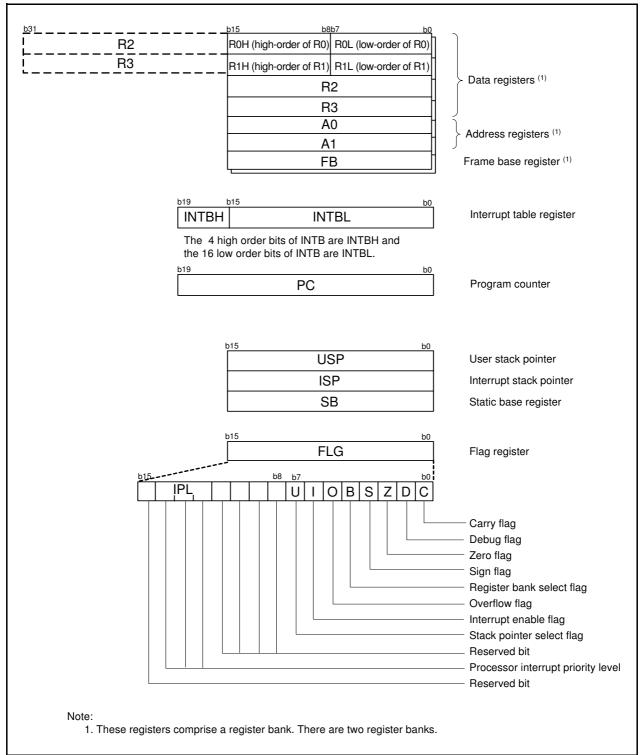

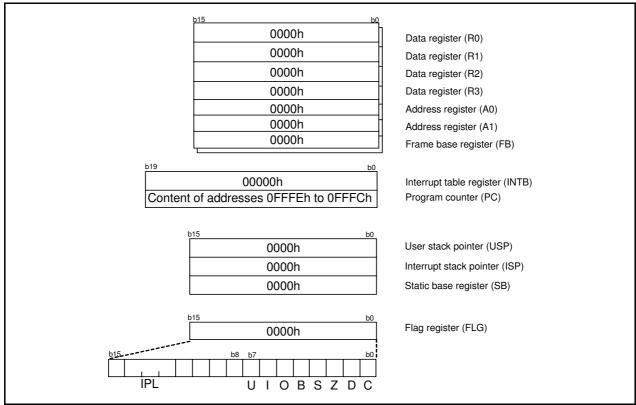

| 2.1        | Data Registers (R0, R1, R2, and R3)                        | 10       |

| 2.2        | Address Registers (A0 and A1)                              |          |

| 2.3        | Frame Base Register (FB)                                   |          |

| 2.4        | Interrupt Table Register (INTB)                            |          |

| 2.5        | Program Counter (PC)                                       |          |

| 2.6        | User Stack Pointer (USP) and Interrupt Stack Pointer (ISP) |          |

| 2.7        | Static Base Register (SB)                                  |          |

| 2.8        | Flag Register (FLG)                                        |          |

| 2.8.1      | Carry Flag (C)                                             |          |

| 2.8.2      | Debug Flag (D)                                             | 10       |

| 2.8.3      | Zero Flag (Z)                                              | 10       |

| 2.8.4      | Sign Flag (S)                                              | 10       |

| 2.8.5      | Register Bank Select Flag (B)                              | 10       |

| 2.8.6      | Overflow Flag (O)                                          | 10       |

| 2.8.7      | Interrupt Enable Flag (I)                                  | 11       |

| 2.8.8      | Stack Pointer Select Flag (U)                              | 11       |

| 2.8.9      | Processor Interrupt Priority Level (IPL)                   | 11       |

| 2.8.10     | Reserved Bit                                               | 11       |

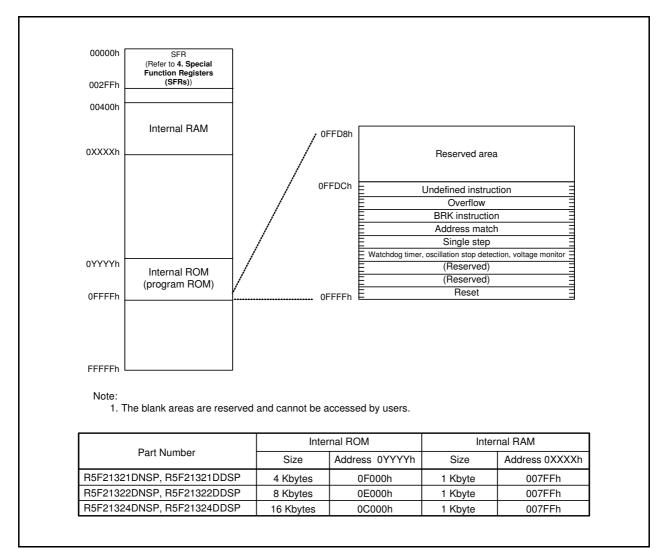

| 3. Me      | emory                                                      | 12       |

| 3.1        | R8C/32D Group                                              |          |

| 3.1        | 100/32B 010up                                              | 12       |

| 4. Sp      | ecial Function Registers (SFRs)                            | 13       |

| 5. Re      | esets                                                      | 22       |

| 5.1        | Registers                                                  |          |

| 5.1.1      | Processor Mode Register 0 (PM0)                            |          |

| 5.1.2      | Reset Source Determination Register (RSTFR)                |          |

| 5.1.2      | Option Function Select Register (OFS)                      |          |

| 5.1.3      | Option Function Select Register 2 (OFS2)                   |          |

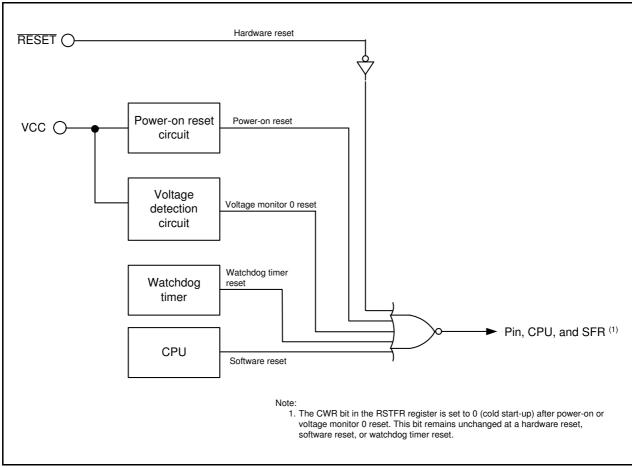

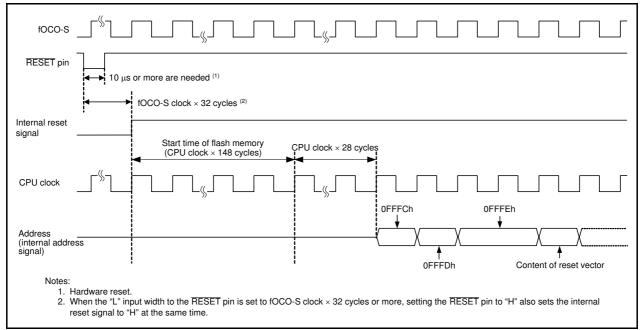

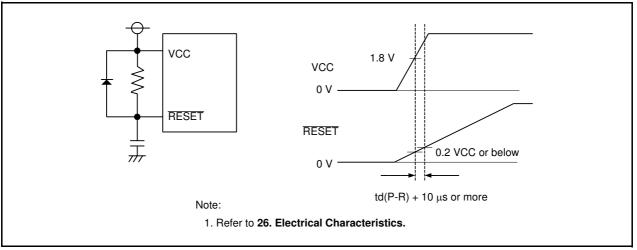

| 5.2        | Hardware Reset                                             |          |

| 5.2.1      | When Power Supply is Stable                                |          |

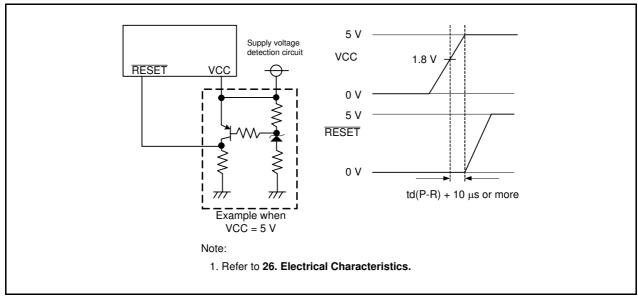

| 5.2.1      | Power On                                                   |          |

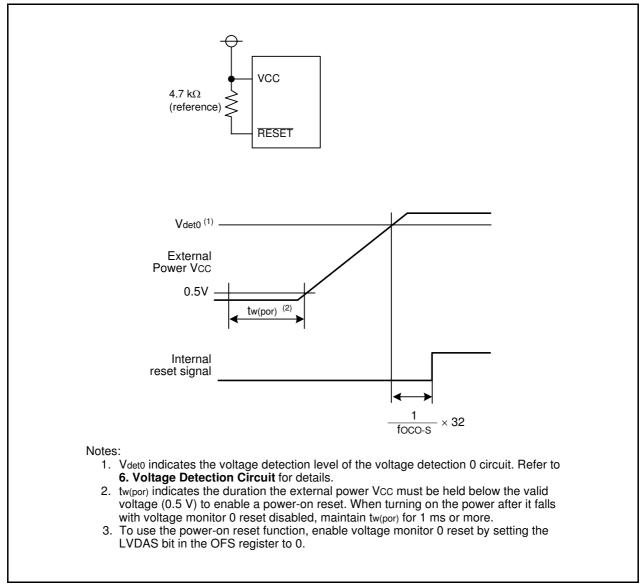

| 5.3        | Power-On Reset Function                                    |          |

| 5.3<br>5.4 | Voltage Monitor 0 Reset                                    |          |

| 5.4<br>5.5 | Watchdog Timer Reset                                       |          |

| 5.5<br>5.6 | Software Reset                                             | 31<br>31 |

|            |                                                            |          |

| 5.7    | Cold Start-Up/Warm Start-Up Determination Function  | 32   |

|--------|-----------------------------------------------------|------|

| 5.8    | Reset Source Determination Function                 | 32   |

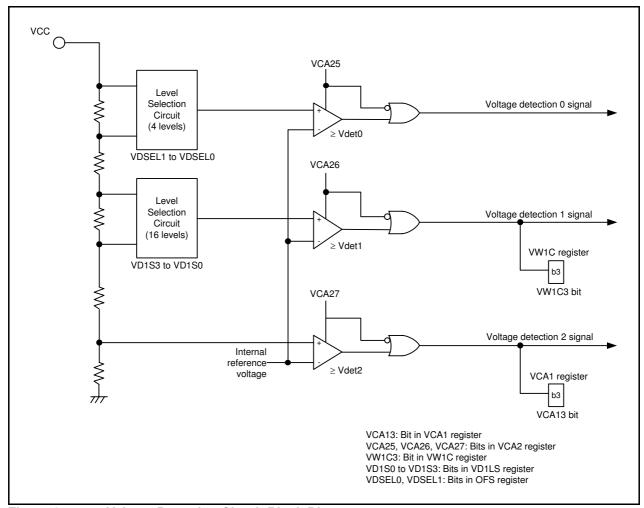

| 6. Vo  | oltage Detection Circuit                            | . 33 |

| 6.1    | Overview                                            |      |

| 6.2    | Registers                                           |      |

| 6.2.1  | Voltage Monitor Circuit Control Register (CMPA)     |      |

| 6.2.2  | Voltage Monitor Circuit Edge Select Register (VCAC) |      |

| 6.2.3  | Voltage Detect Register 1 (VCA1)                    |      |

| 6.2.4  | Voltage Detect Register 2 (VCA2)                    | 39   |

| 6.2.5  | Voltage Detection 1 Level Select Register (VD1LS)   |      |

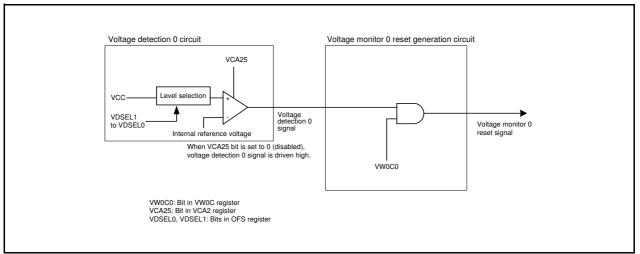

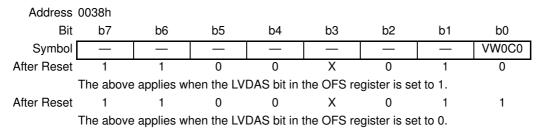

| 6.2.6  | Voltage Monitor 0 Circuit Control Register (VW0C)   | 41   |

| 6.2.7  | Voltage Monitor 1 Circuit Control Register (VW1C)   | 42   |

| 6.2.8  | Voltage Monitor 2 Circuit Control Register (VW2C)   | 43   |

| 6.2.9  | Option Function Select Register (OFS)               | 44   |

| 6.3    | VCC Input Voltage                                   | 45   |

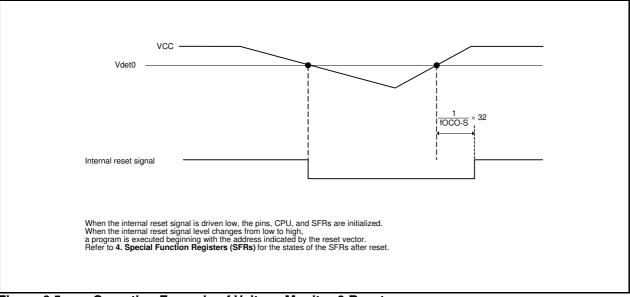

| 6.3.1  | Monitoring Vdet0                                    | 45   |

| 6.3.2  | Monitoring Vdet1                                    | 45   |

| 6.3.3  | Monitoring Vdet2                                    | 45   |

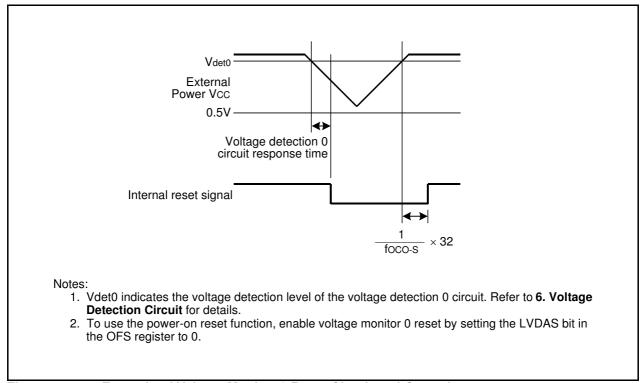

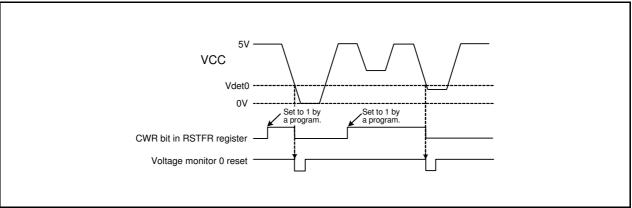

| 6.4    | Voltage Monitor 0 Reset                             | 46   |

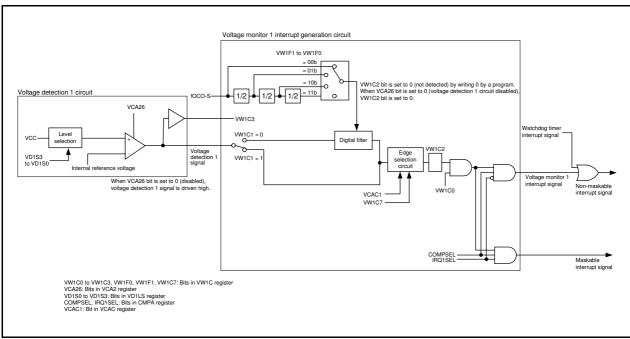

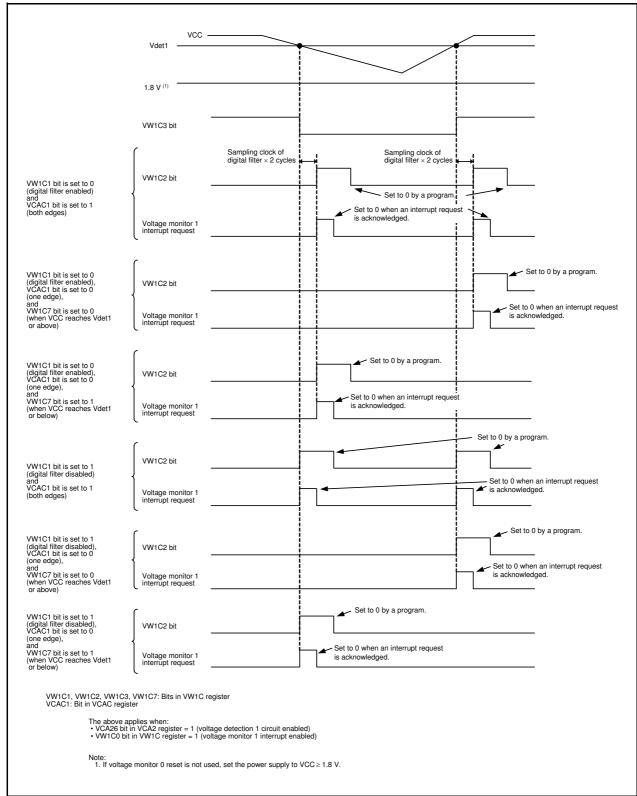

| 6.5    | Voltage Monitor 1 Interrupt                         | 47   |

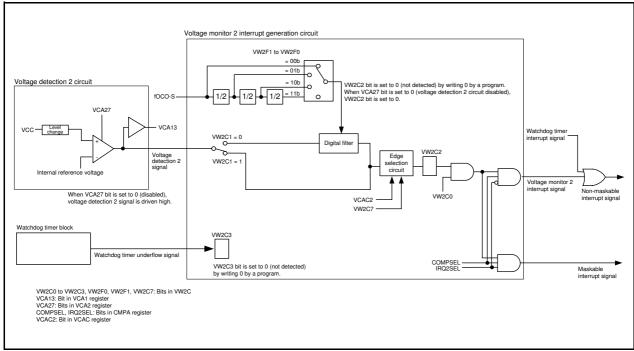

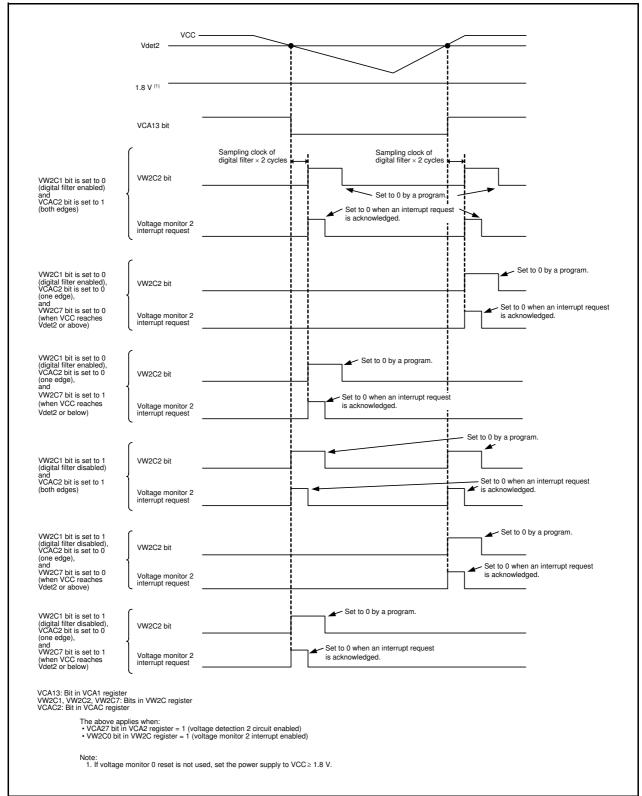

| 6.6    | Voltage Monitor 2 Interrupt                         | 49   |

|        |                                                     |      |

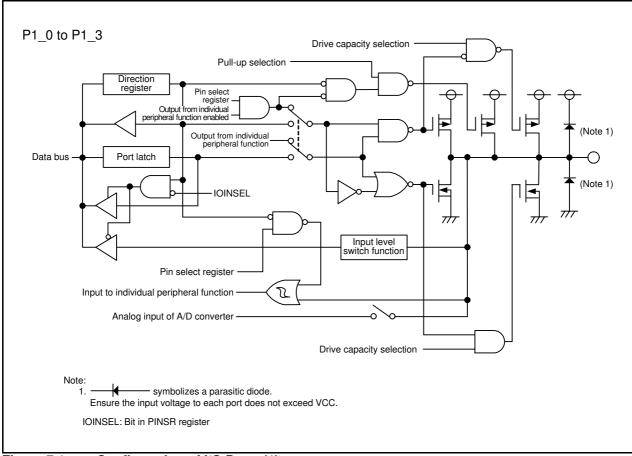

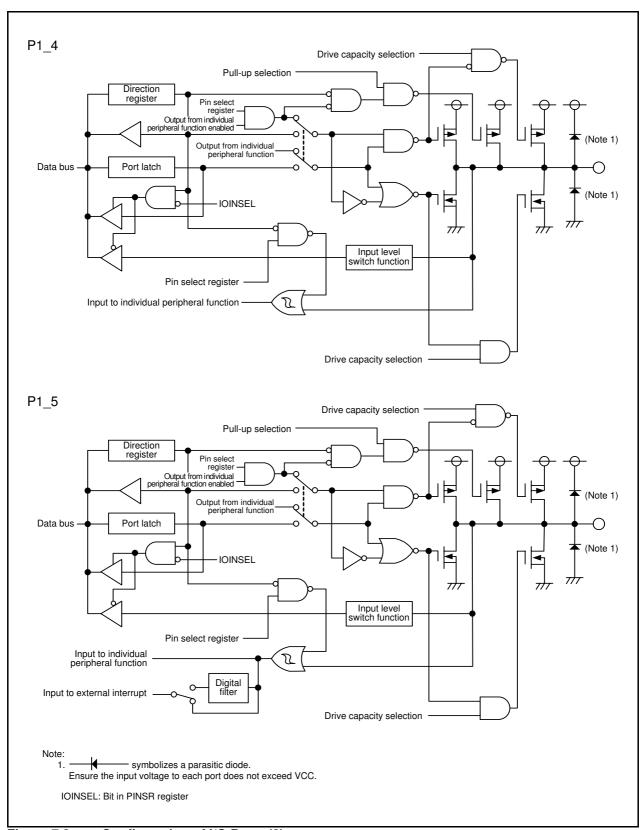

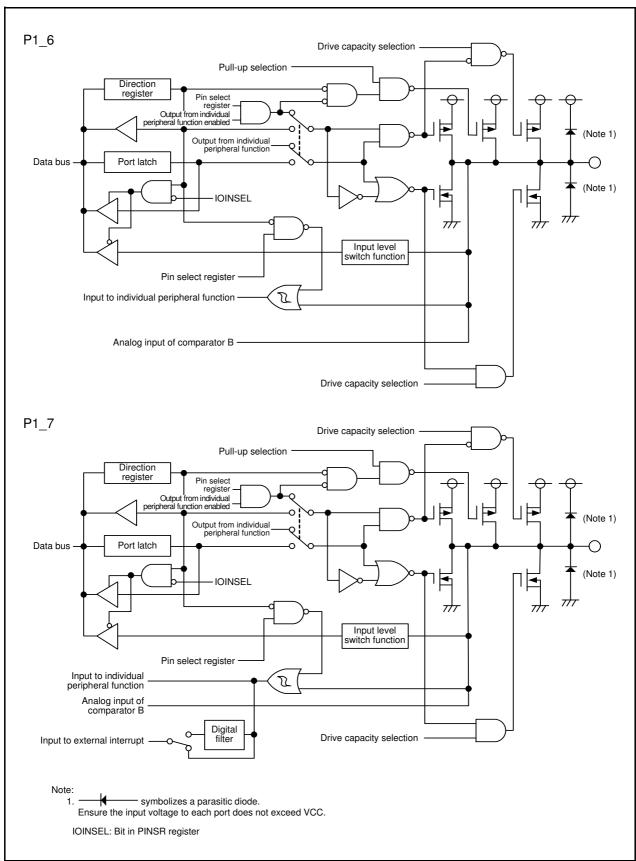

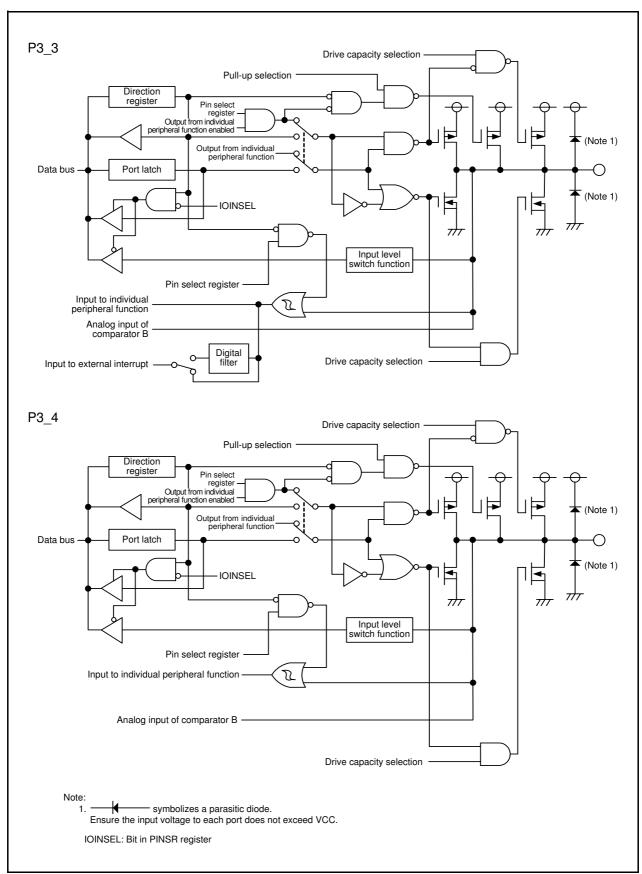

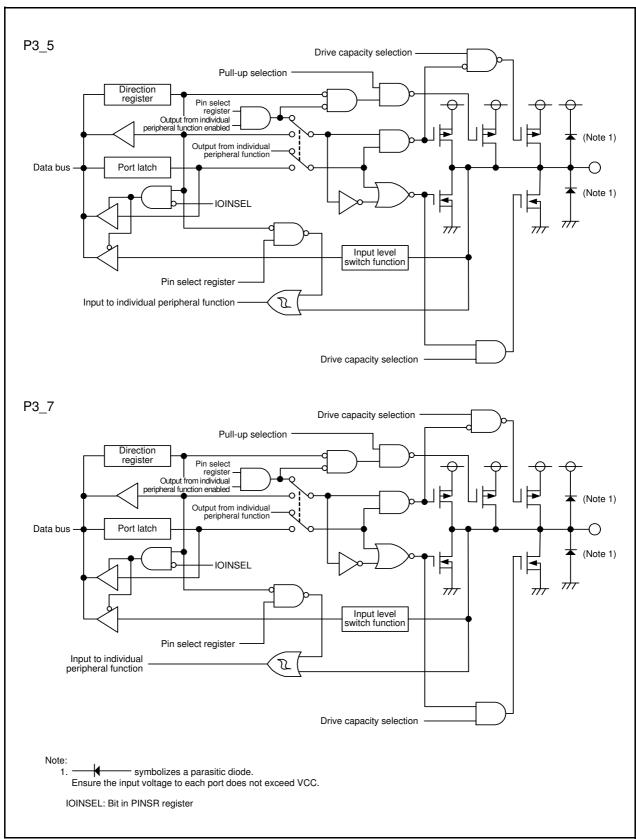

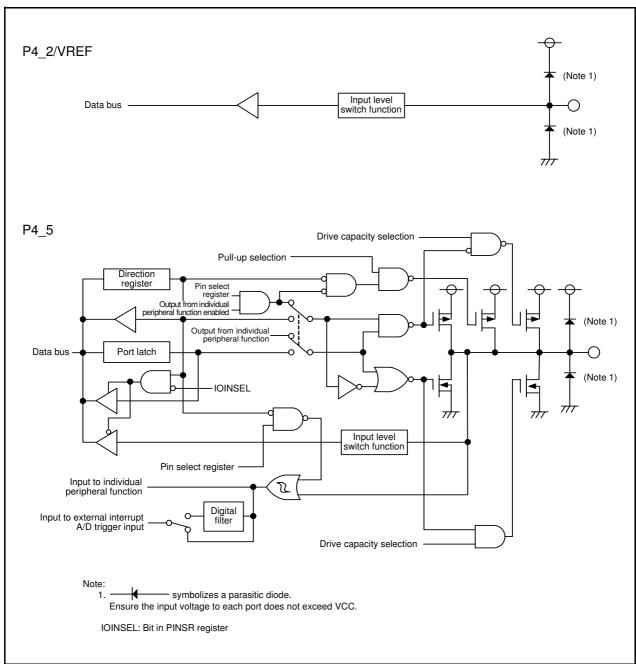

| 7. I/C | ) Ports                                             |      |

| 7.1    | Functions of I/O Ports                              | 51   |

| 7.2    | Effect on Peripheral Functions                      | 52   |

| 7.3    | Pins Other than I/O Ports                           | 52   |

| 7.4    | Registers                                           |      |

| 7.4.1  | Port Pi Direction Register (PDi) (i = 1, 3, 4)      | 61   |

| 7.4.2  | Port Pi Register (Pi) (i = 1, 3, 4)                 | 62   |

| 7.4.3  | Timer RA Pin Select Register (TRASR)                | 63   |

| 7.4.4  | Timer RC Pin Select Register (TRBRCSR)              | 63   |

| 7.4.5  | Timer RC Pin Select Register 0 (TRCPSR0)            | 64   |

| 7.4.6  | Timer RC Pin Select Register 1 (TRCPSR1)            | 64   |

| 7.4.7  | UART0 Pin Select Register (U0SR)                    | 65   |

| 7.4.8  | UART2 Pin Select Register 0 (U2SR0)                 | 65   |

| 7.4.9  | UART2 Pin Select Register 1 (U2SR1)                 | 66   |

| 7.4.10 | O INT Interrupt Input Pin Select Register (INTSR)   | 66   |

| 7.4.1  | 1 I/O Function Pin Select Register (PINSR)          | 67   |

| 7.4.17 | Pull-Up Control Register 0 (PUR0)                   | 68   |

| 7.4.13 | Pull-Up Control Register 1 (PUR1)                   | 68   |

| 7.4.14 |                                                     |      |

| 7.4.13 | 5 Drive Capacity Control Register 0 (DRR0)          | 70   |

| 7.4.10 |                                                     |      |

| 7.4.1  | 7 Input Threshold Control Register 0 (VLT0)         | 71   |

| 7.4.13 | 8 Input Threshold Control Register 1 (VLT1)         | 71   |

| 7.5    | Port Settings                                       | 72   |

| 7.6    | Unassigned Pin Handling                             | 80   |

| 8. E         | Bus                                                     | . 81 |

|--------------|---------------------------------------------------------|------|

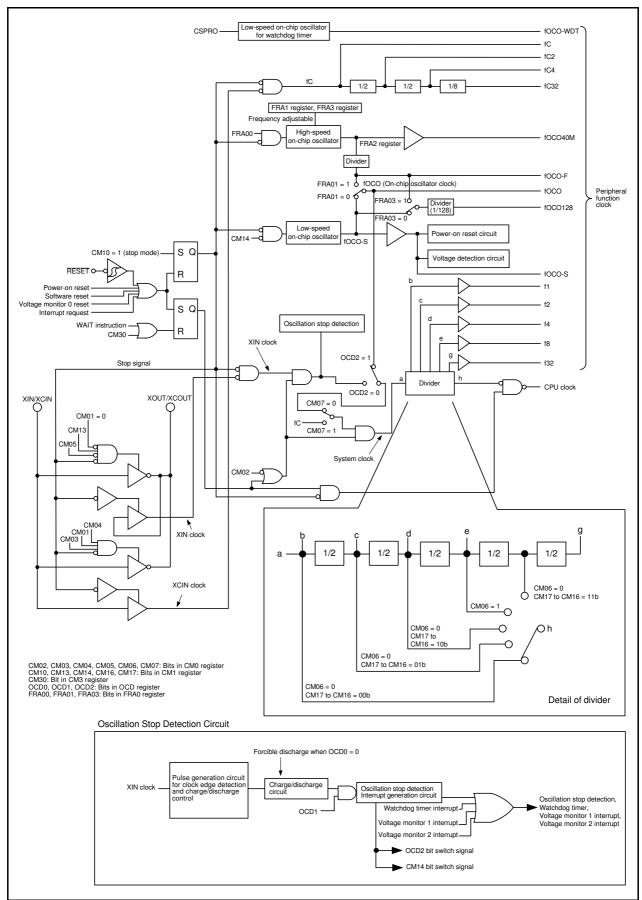

| 9. C         | Nock Generation Circuit                                 | . 83 |

| 9.1          | Overview                                                | 83   |

| 9.2          | Registers                                               | 86   |

| 9.2.         | System Clock Control Register 0 (CM0)                   | 86   |

| 9.2.         | 2 System Clock Control Register 1 (CM1)                 | 87   |

| 9.2.         | 3 System Clock Control Register 3 (CM3)                 | 88   |

| 9.2.         | 4 Oscillation Stop Detection Register (OCD)             | 90   |

| 9.2.         | High-Speed On-Chip Oscillator Control Register 7 (FRA7) | 90   |

| 9.2.         | High-Speed On-Chip Oscillator Control Register 0 (FRA0) | 91   |

| 9.2.         | High-Speed On-Chip Oscillator Control Register 1 (FRA1) | 91   |

| 9.2.         | High-Speed On-Chip Oscillator Control Register 2 (FRA2) | 92   |

| 9.2.         | 9 Clock Prescaler Reset Flag (CPSRF)                    | 92   |

| 9.2.         | High-Speed On-Chip Oscillator Control Register 4 (FRA4) | 93   |

| 9.2.         |                                                         |      |

| 9.2.         |                                                         |      |

| 9.2.         |                                                         |      |

| 9.2.         |                                                         |      |

| 9.3          | XIN Clock                                               |      |

| 9.4          | On-Chip Oscillator Clock                                |      |

| 9.4.         | r                                                       |      |

| 9.4.         |                                                         |      |

| 9.5          | XCIN Clock                                              |      |

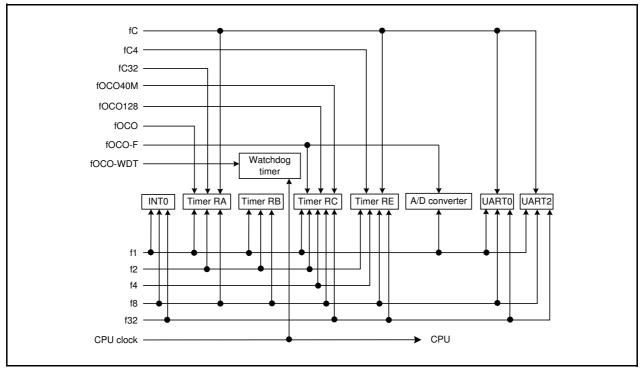

| 9.6          | CPU Clock and Peripheral Function Clock                 |      |

| 9.6.         | - <b>,</b>                                              |      |

| 9.6.         |                                                         |      |

| 9.6.         |                                                         |      |

| 9.6.         |                                                         |      |

| 9.6.         |                                                         |      |

| 9.6.         |                                                         |      |

| 9.6.<br>9.6. |                                                         |      |

| 9.6.         |                                                         |      |

| 9.6.         |                                                         |      |

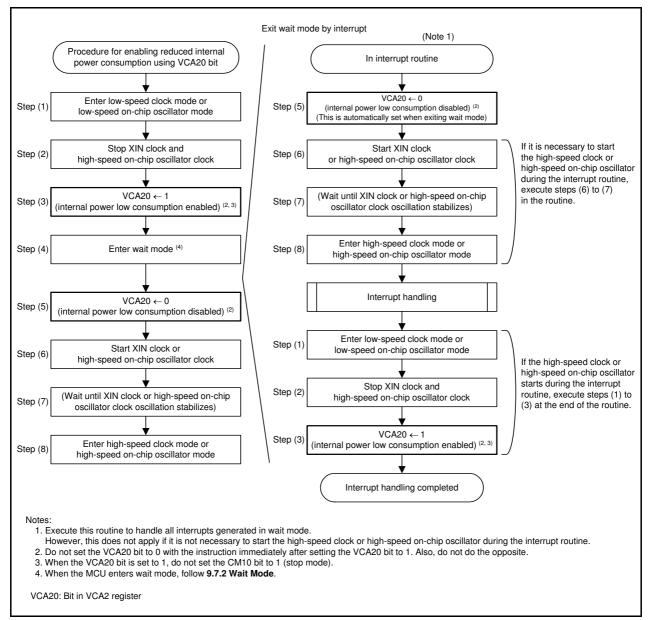

| 9.0.<br>9.7  | Power Control                                           |      |

| 9.7.<br>9.7. |                                                         |      |

| 9.7.         | • •                                                     |      |

| 9.7.         |                                                         |      |

| 9.8          | Oscillation Stop Detection Function                     |      |

| 9.8.         | •                                                       |      |

| 9.9          | Notes on Clock Generation Circuit                       |      |

| 9.9.         |                                                         |      |

| 9.9.         | •                                                       |      |

| 9.9.         |                                                         |      |

| 9.9.         | •                                                       |      |

| 10. F        | Protection                                              | 116  |

| 10.1         | Register                                                | 116  |

| 10.1.1           | Protect Register (PRCR)                                                                      | 116   |

|------------------|----------------------------------------------------------------------------------------------|-------|

| 11. Inte         | errupts                                                                                      | 117   |

| 11.1             | Overview                                                                                     | 117   |

| 11.1.1           | Types of Interrupts                                                                          |       |

| 11.1.2           | 71                                                                                           |       |

| 11.1.3           | •                                                                                            |       |

| 11.1.4           |                                                                                              |       |

| 11.1.5           |                                                                                              |       |

| 11.2             | Registers                                                                                    |       |

| 11.2.1           |                                                                                              | P1IC, |

| 11.2.2           | · ·                                                                                          |       |

| 11.2.3           | INTi Interrupt Control Register (INTiIC) (i = 0, 1, 3)                                       | 124   |

| 11.3             | Interrupt Control                                                                            | 125   |

| 11.3.1           | I Flag                                                                                       | 125   |

| 11.3.2           | IR Bit                                                                                       | 125   |

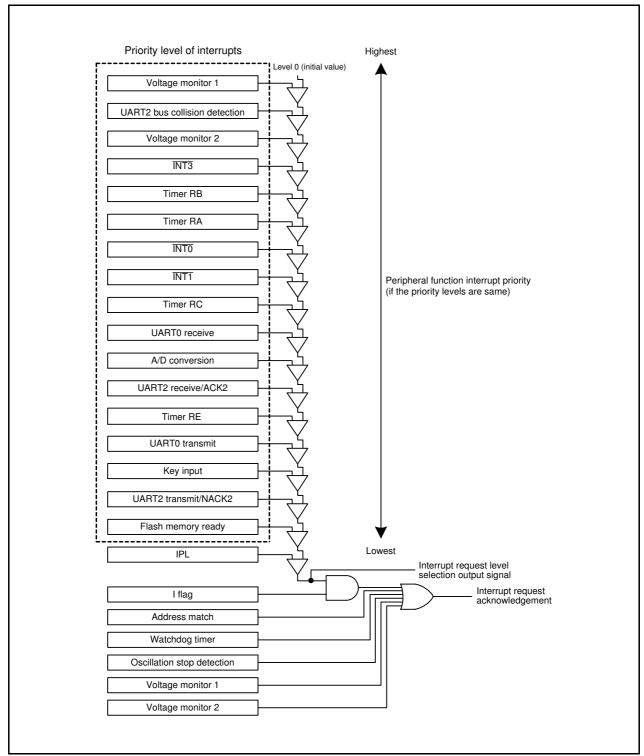

| 11.3.3           | Bits ILVL2 to ILVL0, IPL                                                                     | 125   |

| 11.3.4           | Interrupt Sequence                                                                           | 126   |

| 11.3.5           | Interrupt Response Time                                                                      | 127   |

| 11.3.6           | IPL Change when Interrupt Request is Acknowledged                                            | 127   |

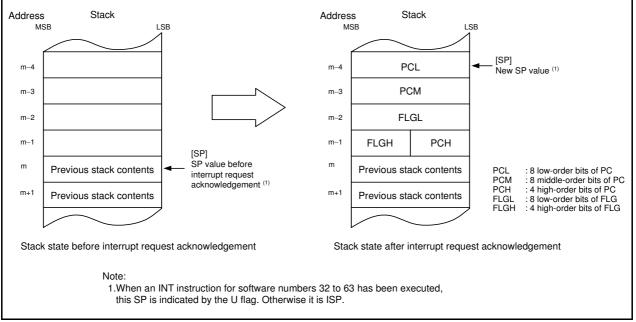

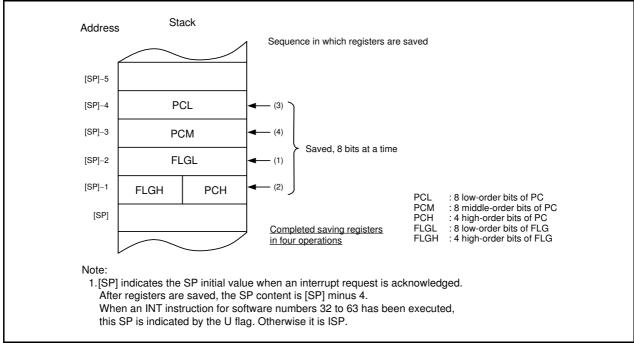

| 11.3.7           | Saving Registers                                                                             | 128   |

| 11.3.8           | Returning from Interrupt Routine                                                             | 130   |

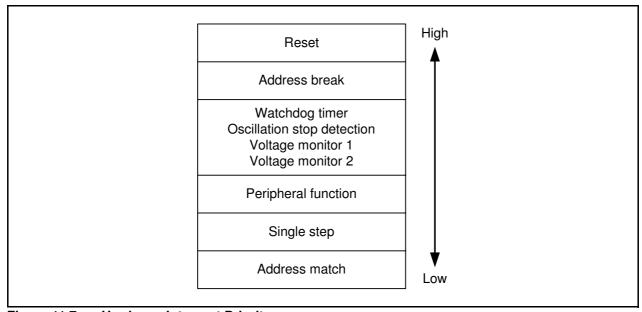

| 11.3.9           | Interrupt Priority                                                                           | 130   |

| 11.3.1           | · · · · · · · · · · · · · · · · · · ·                                                        |       |

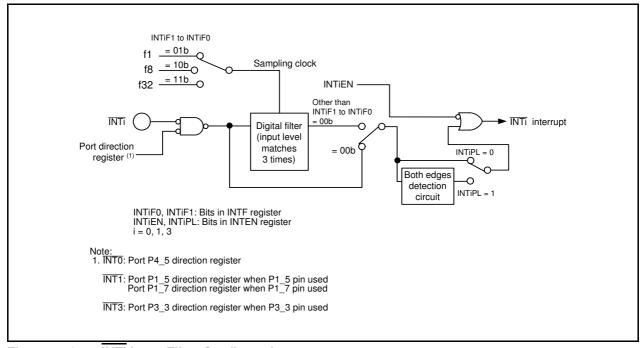

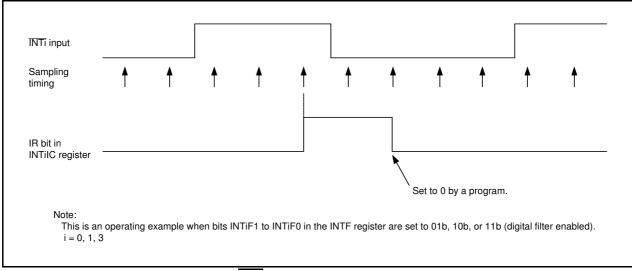

| 11.4             | INT Interrupt                                                                                | 132   |

| 11.4.1           |                                                                                              |       |

| 11.4.2           |                                                                                              |       |

| 11.4.3           |                                                                                              |       |

| 11.4.4           |                                                                                              |       |

| 11.4.5           |                                                                                              |       |

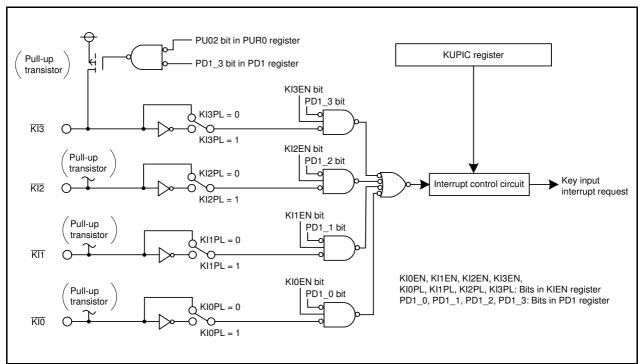

|                  | Key Input Interrupt                                                                          |       |

| 11.5.1           |                                                                                              |       |

| 11.6             | Address Match Interrupt                                                                      |       |

| 11.6.1           | Address Match Interrupt Enable Register (AIER)                                               |       |

| 11.6.2           |                                                                                              |       |

| 11.7             | Timer RC Interrupt and Flash Memory Interrupt (Interrupts with Multiple Interrupt Request So |       |

| 11.8             | Notes on Interments                                                                          |       |

|                  | Notes on Interrupts                                                                          |       |

| 11.8.1<br>11.8.2 | Reading Address 00000h                                                                       |       |

| 11.8.2           | C                                                                                            |       |

| 11.8.3           |                                                                                              |       |

| 11.8.4           |                                                                                              |       |

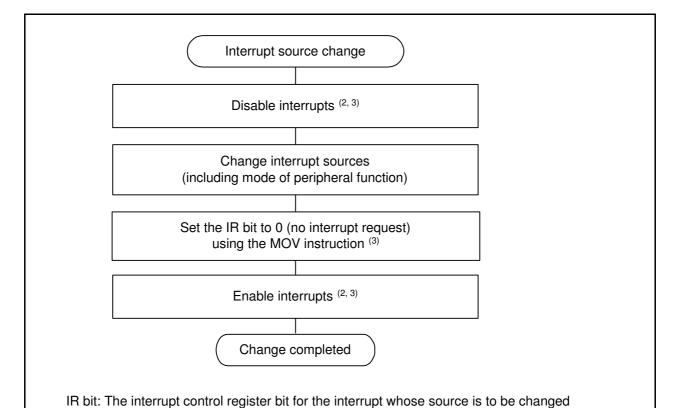

| 11.0.3           | Rewriting Interrupt Control Register                                                         | 143   |

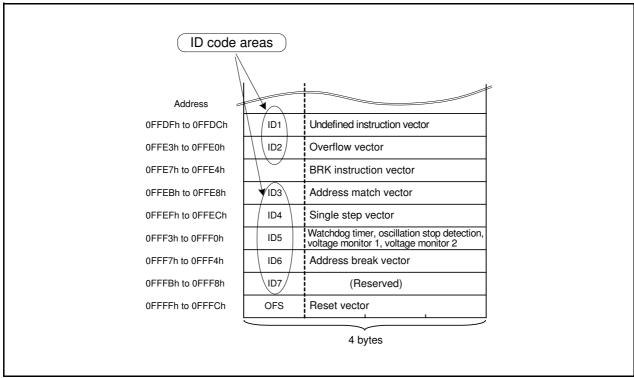

| 12. ID           | Code Areas                                                                                   | 144   |

| 12.1             | Overview                                                                                     | 144   |

| 10.0             | Eunstians                                                                                    | 1.45  |

| 12.3 Forced Erase Function                                                    | 146 |

|-------------------------------------------------------------------------------|-----|

| 12.4 Standard Serial I/O Mode Disabled Function                               | 146 |

| 12.5 Notes on ID Code Areas                                                   | 147 |

| 12.5.1 Setting Example of ID Code Areas                                       | 147 |

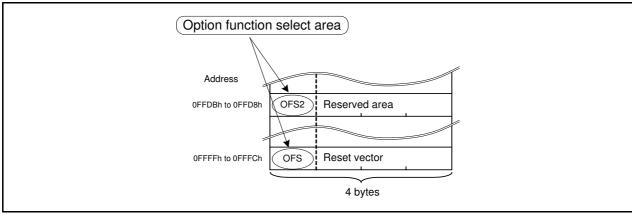

| 13. Option Function Select Area                                               | 148 |

| 13.1 Overview                                                                 | 148 |

| 13.2 Registers                                                                |     |

| 13.2.1 Option Function Select Register (OFS)                                  |     |

| 13.2.2 Option Function Select Register 2 (OFS2)                               |     |

| 13.3 Notes on Option Function Select Area                                     |     |

| 13.3.1 Setting Example of Option Function Select Area                         | 151 |

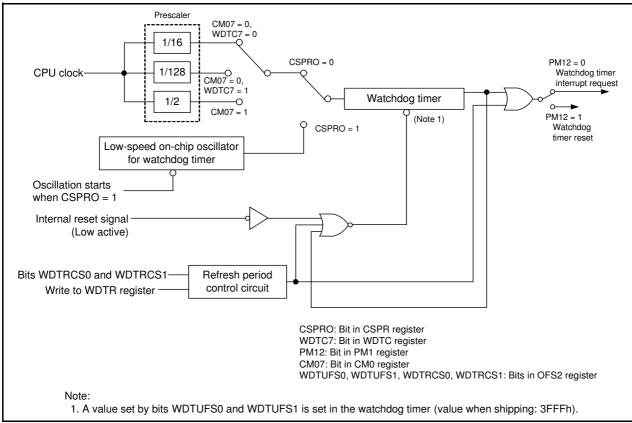

| 14. Watchdog Timer                                                            | 152 |

| 14.1 Overview                                                                 |     |

| 14.2 Registers                                                                |     |

| 14.2.1 Processor Mode Register 1 (PM1)                                        |     |

| 14.2.2 Watchdog Timer Reset Register (WDTR)                                   |     |

| 14.2.3 Watchdog Timer Start Register (WDTS)                                   |     |

| 14.2.4 Watchdog Timer Control Register (WDTC)                                 |     |

| 14.2.5 Count Source Protection Mode Register (CSPR)                           |     |

| 14.2.6 Option Function Select Register (OFS)                                  | 156 |

| 14.2.7 Option Function Select Register 2 (OFS2)                               | 157 |

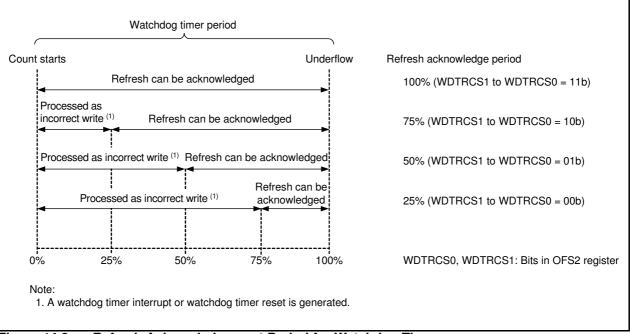

| 14.3 Functional Description                                                   | 158 |

| 14.3.1 Common Items for Multiple Modes                                        | 158 |

| 14.3.2 Count Source Protection Mode Disabled                                  | 159 |

| 14.3.3 Count Source Protection Mode Enabled                                   | 160 |

| 15. General Overview of Timers                                                | 161 |

| 16. Timer RA                                                                  | 163 |

| 16.1 Overview                                                                 |     |

| 16.2 Registers                                                                |     |

| 16.2.1 Timer RA Control Register (TRACR)                                      |     |

| 16.2.2 Timer RA I/O Control Register (TRAIOC)                                 |     |

| 16.2.3 Timer RA Mode Register (TRAMR)                                         |     |

| 16.2.4 Timer RA Prescaler Register (TRAPRE)                                   |     |

| 16.2.5 Timer RA Register (TRA)                                                |     |

| 16.2.6 Timer RA Pin Select Register (TRASR)                                   |     |

| 16.3 Timer Mode                                                               |     |

| 16.3.1 Timer RA I/O Control Register (TRAIOC) in Timer Mode                   |     |

| 16.3.2 Timer Write Control during Count Operation                             |     |

| 16.4 Pulse Output Mode                                                        |     |

| 16.4.1 Timer RA I/O Control Register (TRAIOC) in Pulse Output Mode            |     |

| 16.5 Event Counter Mode                                                       |     |

| 16.5.1 Timer RA I/O Control Register (TRAIOC) in Event Counter Mode           | 172 |

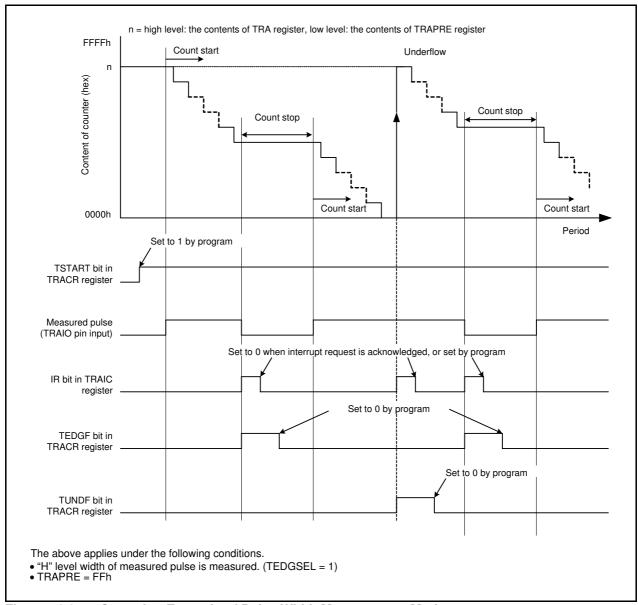

| 16.6 Pulse Width Measurement Mode                                             |     |

| 16.6.1 Timer RA I/O Control Register (TRAIOC) in Pulse Width Measurement Mode | 174 |

| 16.6.2 Operating Example                                                      | 175 |

| 16.7    | Pulse Period Measurement Mode                                                        | 176        |

|---------|--------------------------------------------------------------------------------------|------------|

| 16.7.1  | Timer RA I/O Control Register (TRAIOC) in Pulse Period Measurement Mode              | 177        |

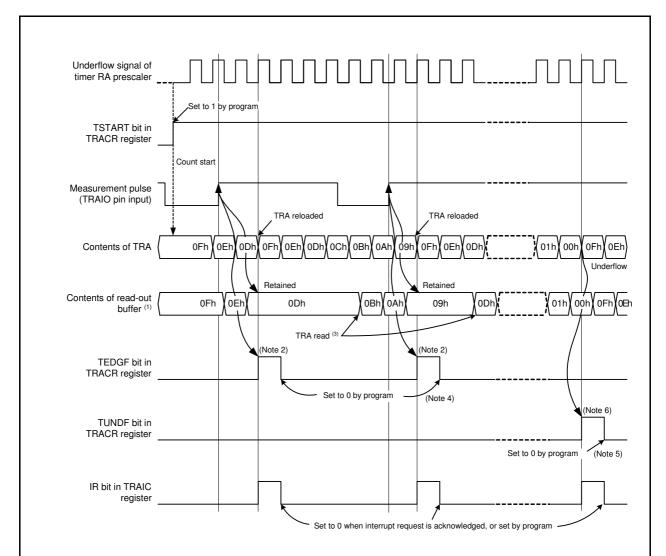

| 16.7.2  | Operating Example                                                                    | 178        |

| 16.8    | Notes on Timer RA                                                                    | 179        |

|         |                                                                                      |            |

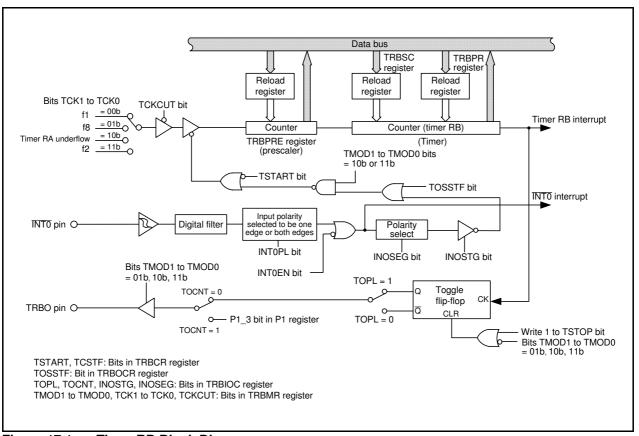

| 17. Tim | er RB                                                                                | 180        |

| 17.1    | Overview                                                                             | 180        |

| 17.2    | Registers                                                                            | 181        |

| 17.2.1  | Timer RB Control Register (TRBCR)                                                    | 181        |

| 17.2.2  | Timer RB One-Shot Control Register (TRBOCR)                                          | 181        |

| 17.2.3  | Timer RB I/O Control Register (TRBIOC)                                               | 182        |

| 17.2.4  | Timer RB Mode Register (TRBMR)                                                       | 182        |

| 17.2.5  | Timer RB Prescaler Register (TRBPRE)                                                 | 183        |

| 17.2.6  | Timer RB Secondary Register (TRBSC)                                                  | 183        |

| 17.2.7  | Timer RB Primary Register (TRBPR)                                                    | 184        |

| 17.3    | Timer Mode                                                                           | 185        |

| 17.3.1  | Timer RB I/O Control Register (TRBIOC) in Timer Mode                                 | 185        |

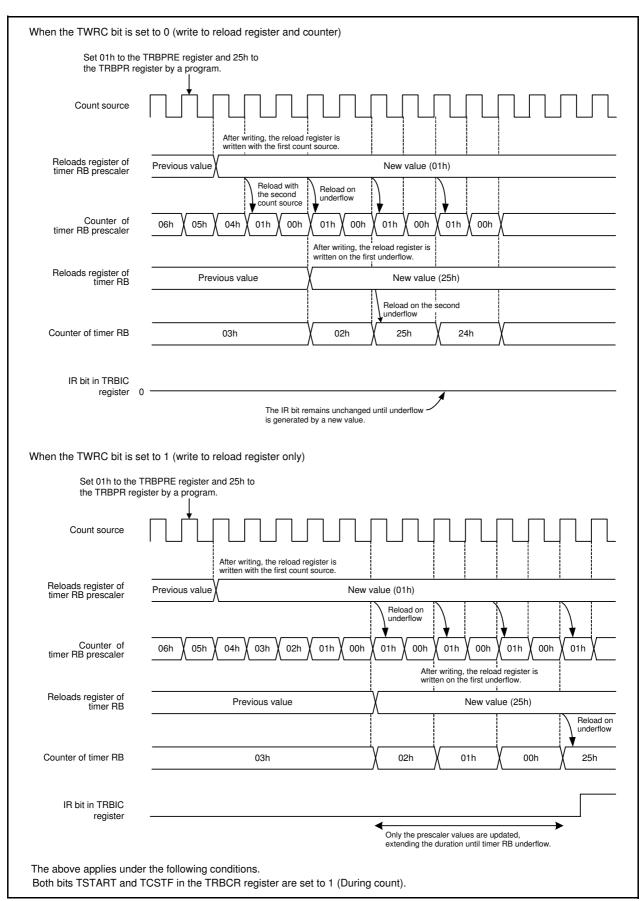

| 17.3.2  | Timer Write Control during Count Operation                                           | 186        |

| 17.4    | Programmable Waveform Generation Mode                                                | 188        |

| 17.4.1  | Timer RB I/O Control Register (TRBIOC) in Programmable Waveform Generation Mode      |            |

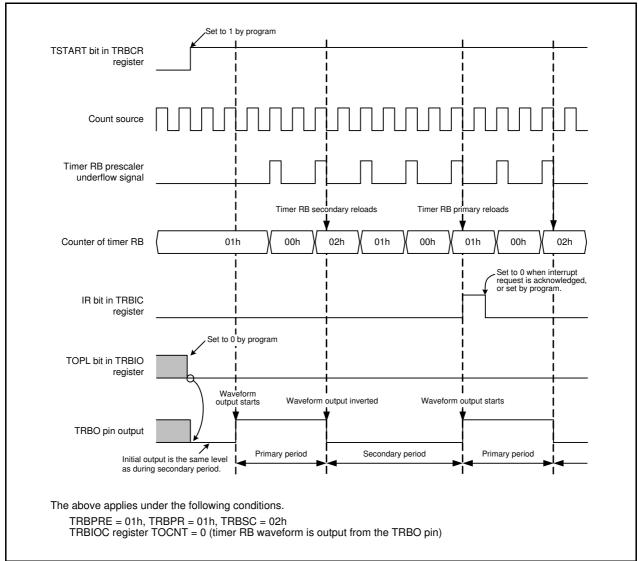

| 17.4.2  | Operating Example                                                                    |            |

|         | Programmable One-shot Generation Mode                                                |            |

| 17.5.1  | Timer RB I/O Control Register (TRBIOC) in Programmable One-Shot Generation Mode      |            |

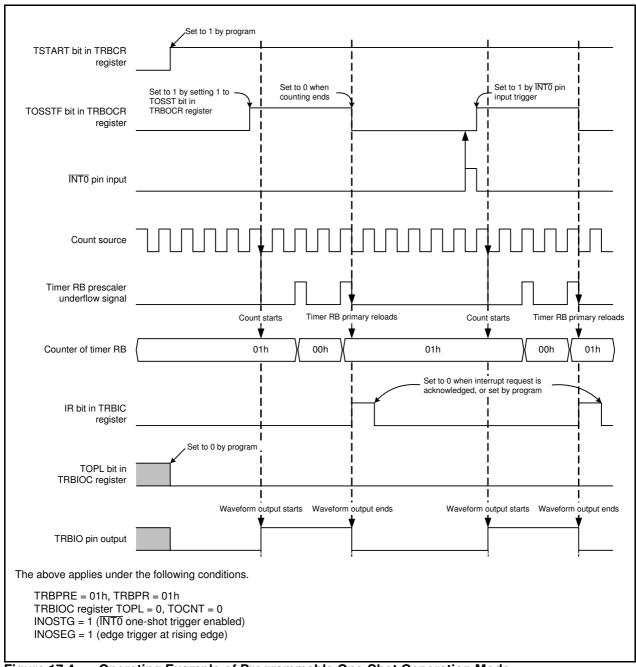

| 17.5.2  | Operating Example                                                                    |            |

| 17.5.3  | One-Shot Trigger Selection                                                           |            |

|         | Programmable Wait One-Shot Generation Mode                                           |            |

| 17.6.1  | Timer RB I/O Control Register (TRBIOC) in Programmable Wait One-Shot Generation Mode |            |

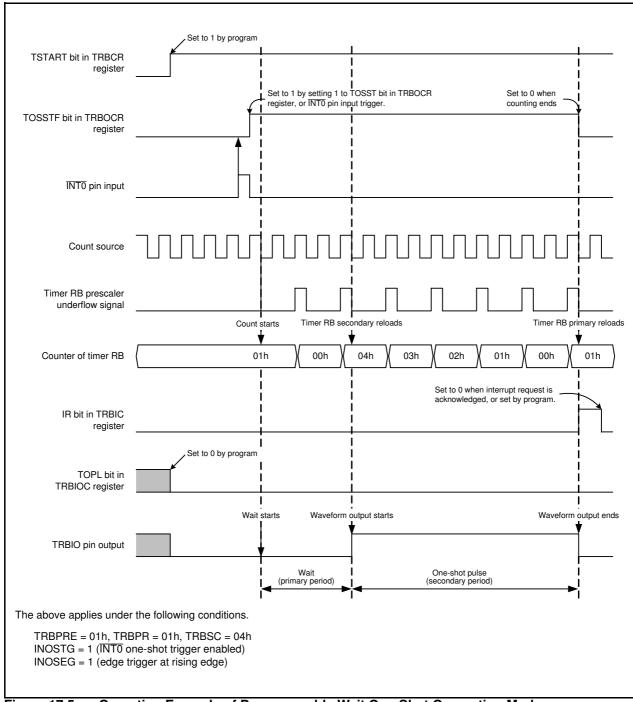

| 17.6.2  | Operating Example                                                                    |            |

| 17.7    | Notes on Timer RB                                                                    |            |

| 17.7.1  | Timer Mode                                                                           |            |

| 17.7.2  | Programmable Waveform Generation Mode                                                |            |

| 17.7.2  | Programmable One-shot Generation Mode                                                |            |

| 17.7.3  | Programmable Wait One-shot Generation Mode                                           |            |

| 17.7.4  | Trogrammable wait one shot denoration blode                                          | 177        |

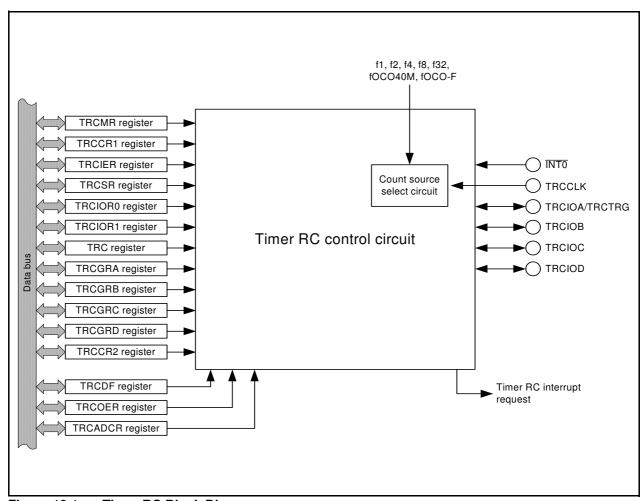

| 18. Tim | er RC                                                                                | 200        |

| 18.1    | Overview                                                                             | 200        |

|         | Registers                                                                            |            |

| 18.2.1  | Module Standby Control Register (MSTCR)                                              |            |

| 18.2.2  | Timer RC Mode Register (TRCMR)                                                       |            |

| 18.2.3  | Timer RC Control Register 1 (TRCCR1)                                                 |            |

| 18.2.4  | Timer RC Interrupt Enable Register (TRCIER)                                          |            |

| 18.2.5  | Timer RC Status Register (TRCSR)                                                     |            |

| 18.2.6  | Timer RC I/O Control Register 0 (TRCIOR0)                                            |            |

| 18.2.7  | Timer RC I/O Control Register 1 (TRCIOR1)                                            |            |

| 18.2.8  | Timer RC Counter (TRC)                                                               |            |

| 18.2.9  | Timer RC General Registers A, B, C, and D (TRCGRA, TRCGRB, TRCGRC, TRCGRD)           |            |

| 18.2.10 |                                                                                      |            |

| 18.2.1  |                                                                                      |            |

| 18.2.1  |                                                                                      | 200<br>209 |

| 10/1    | C. THURLING AND ADDUCTIVANCE CHADIC NEVINCE CLING VICA I                             | /119       |

| 18.2.13          | Timer RC Trigger Control Register (TRCADCR)                                                                                 | 209 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|

| 18.2.14          | Timer RC Pin Select Register (TRBRCSR)                                                                                      | 210 |

| 18.2.15          | Timer RC Pin Select Register 0 (TRCPSR0)                                                                                    | 211 |

| 18.2.16          | Timer RC Pin Select Register 1 (TRCPSR1)                                                                                    | 211 |

| 18.3             | Common Items for Multiple Modes                                                                                             | 212 |

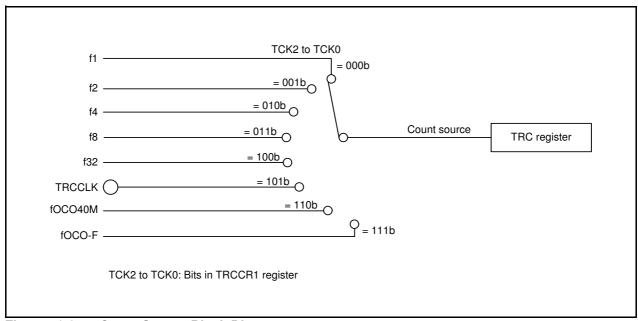

| 18.3.1           | Count Source                                                                                                                | 212 |

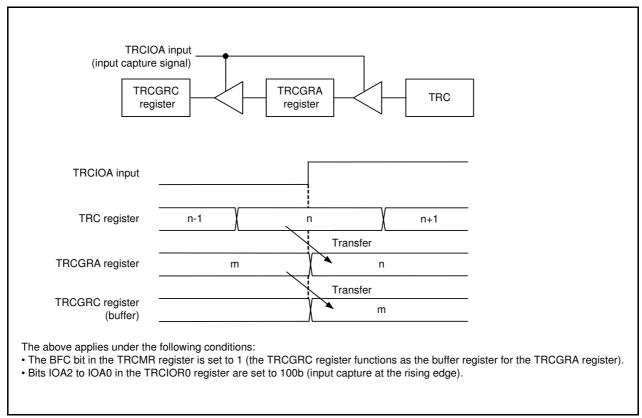

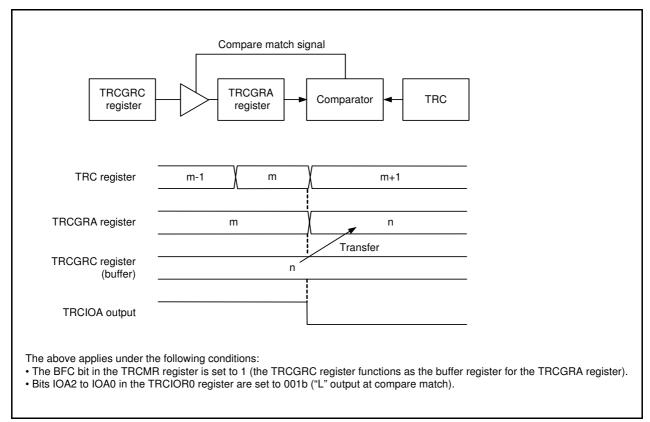

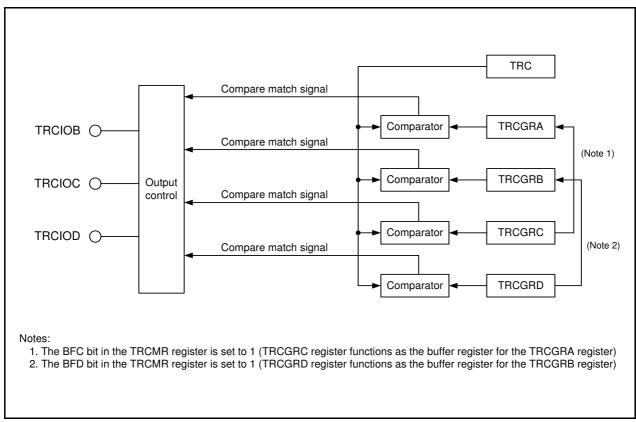

| 18.3.2           | Buffer Operation                                                                                                            | 213 |

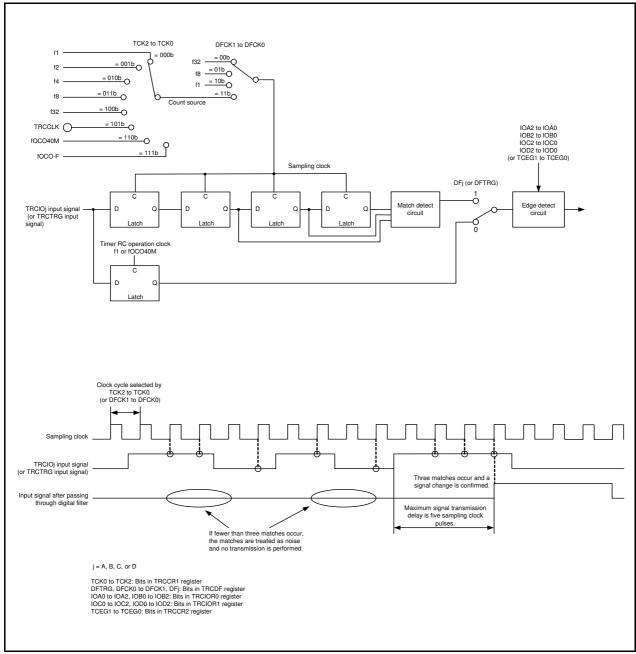

| 18.3.3           | Digital Filter                                                                                                              | 215 |

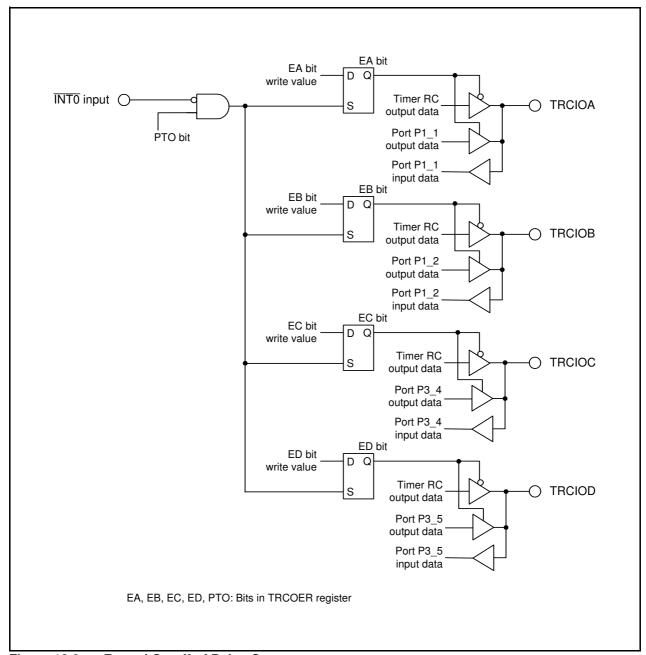

| 18.3.4           | Forced Cutoff of Pulse Output                                                                                               | 216 |

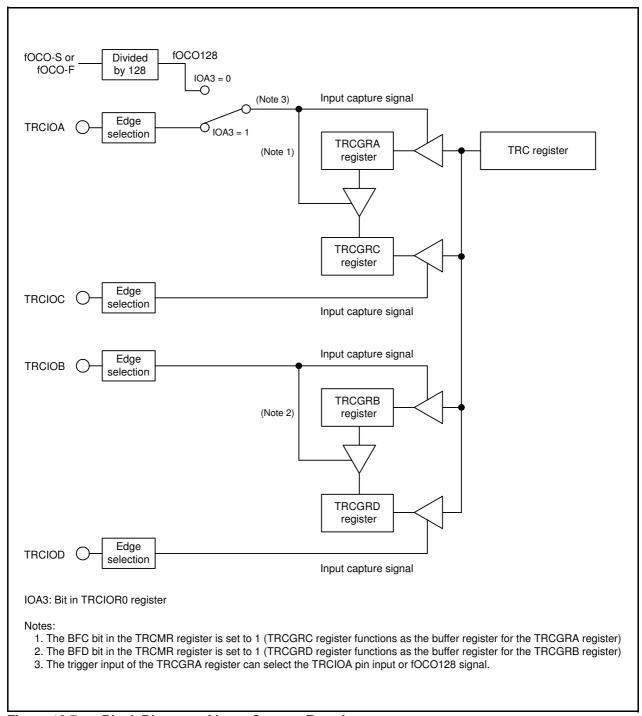

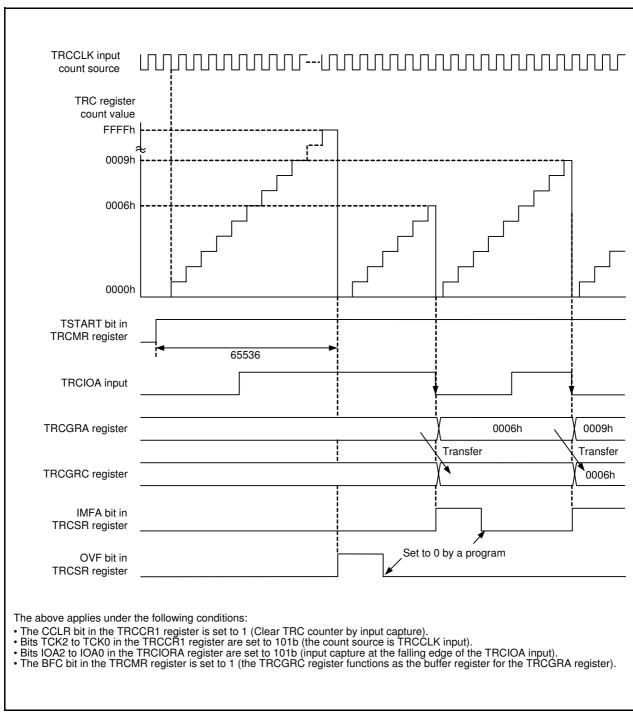

| 18.4             | Timer Mode (Input Capture Function)                                                                                         | 218 |

| 18.4.1           | Timer RC I/O Control Register 0 (TRCIOR0) for Input Capture Function                                                        | 220 |

| 18.4.2           | Timer RC I/O Control Register 1 (TRCIOR1) for Input Capture Function                                                        | 221 |

| 18.4.3           | Operating Example                                                                                                           | 222 |

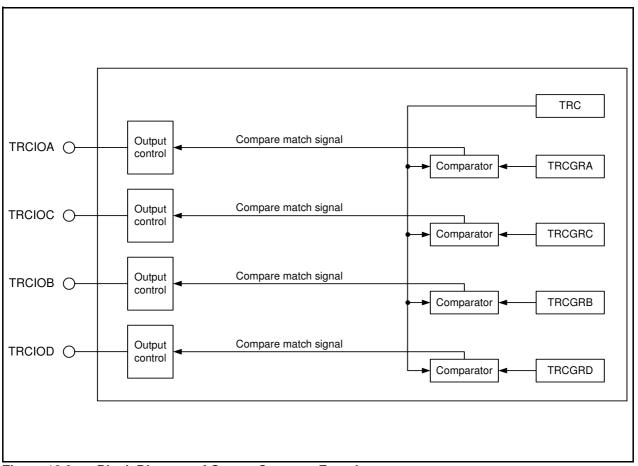

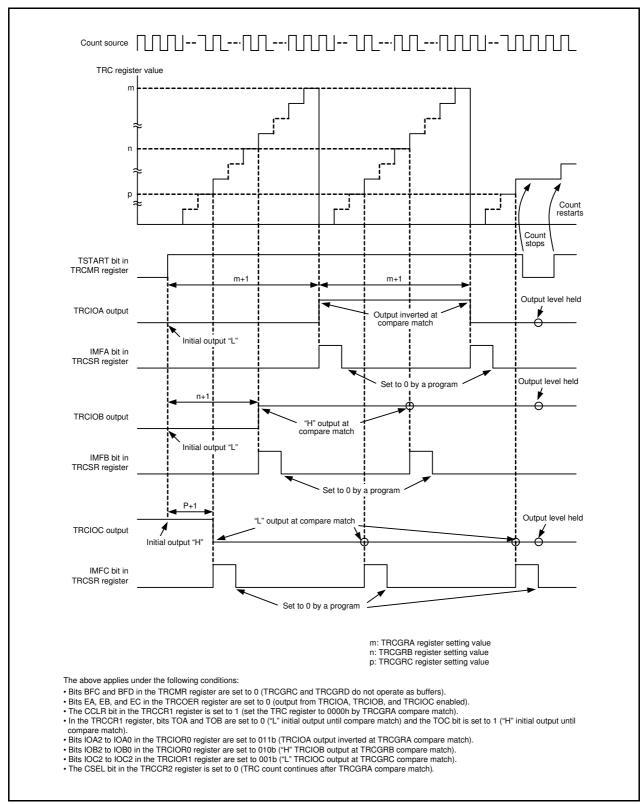

| 18.5             | Timer Mode (Output Compare Function)                                                                                        | 223 |

| 18.5.1           | Timer RC Control Register 1 (TRCCR1) for Output Compare Function                                                            | 225 |

| 18.5.2           | Timer RC I/O Control Register 0 (TRCIOR0) for Output Compare Function                                                       | 226 |

| 18.5.3           | Timer RC I/O Control Register 1 (TRCIOR1) for Output Compare Function                                                       | 227 |

| 18.5.4           | Timer RC Control Register 2 (TRCCR2) for Output Compare Function                                                            | 228 |

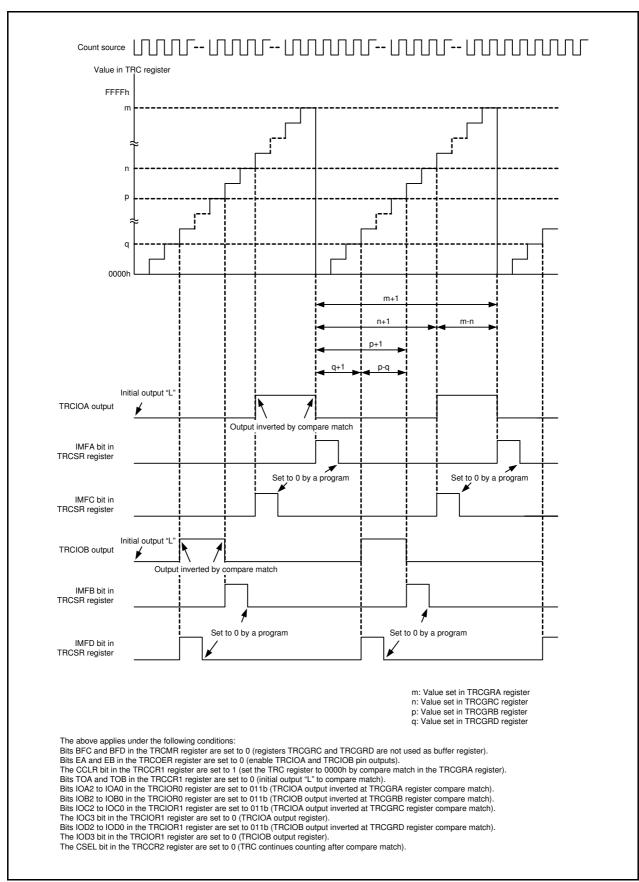

| 18.5.5           | Operating Example                                                                                                           | 229 |

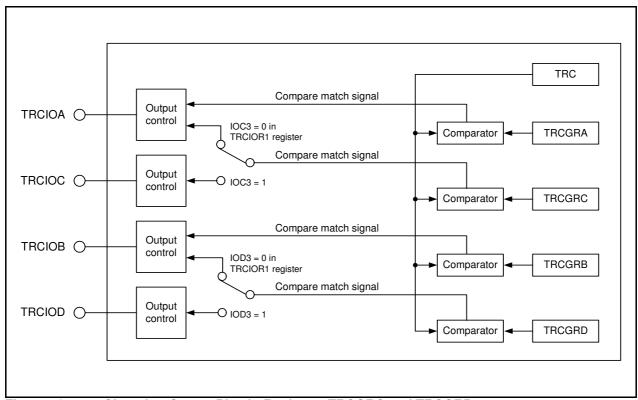

| 18.5.6           | Changing Output Pins in Registers TRCGRC and TRCGRD                                                                         | 230 |

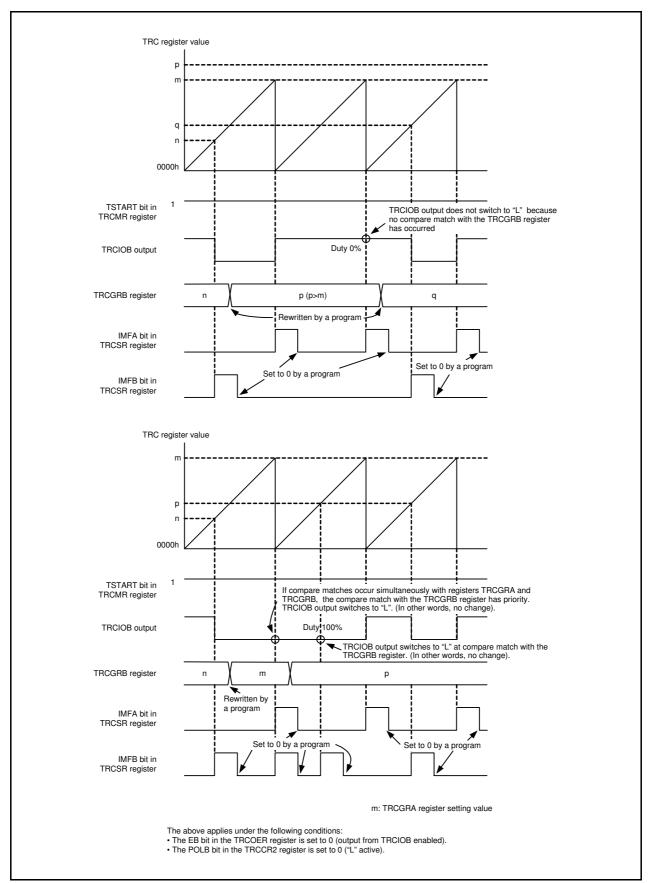

| 18.6             | PWM Mode                                                                                                                    | 232 |

| 18.6.1           | Timer RC Control Register 1 (TRCCR1) in PWM Mode                                                                            | 234 |

| 18.6.2           | Timer RC Control Register 2 (TRCCR2) in PWM Mode                                                                            | 234 |

| 18.6.3           | Operating Example                                                                                                           | 236 |

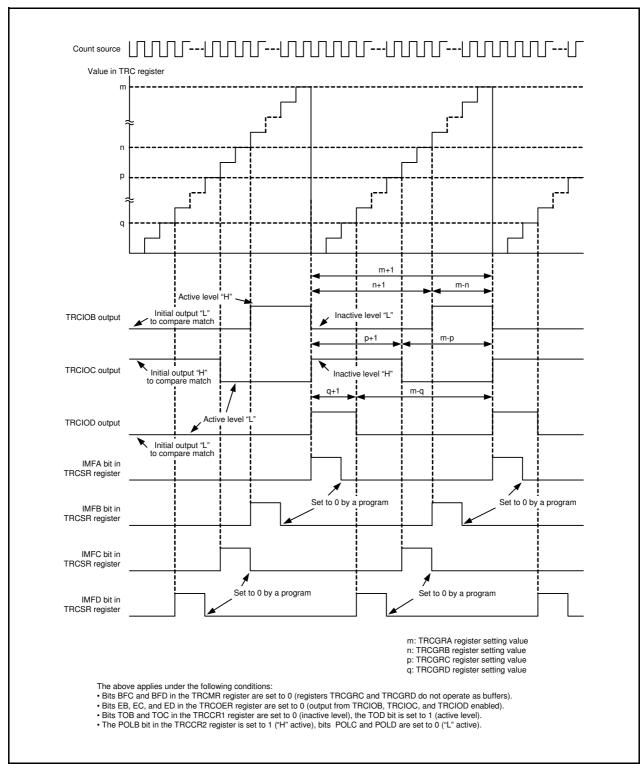

| 18.7             | PWM2 Mode                                                                                                                   | 238 |

| 18.7.1           | Timer RC Control Register 1 (TRCCR1) in PWM2 Mode                                                                           | 240 |

| 18.7.2           | Timer RC Control Register 2 (TRCCR2) in PWM2 Mode                                                                           | 241 |

| 18.7.3           | Timer RC Digital Filter Function Select Register (TRCDF) in PWM2 Mode                                                       | 241 |

| 18.7.4           | Operating Example                                                                                                           | 243 |

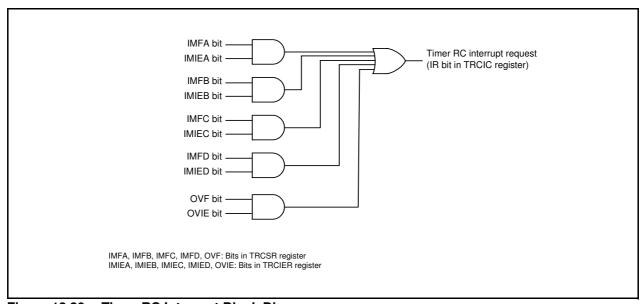

| 18.8             | Timer RC Interrupt                                                                                                          | 246 |

| 18.9             | Notes on Timer RC                                                                                                           | 247 |

| 18.9.1           | TRC Register                                                                                                                | 247 |

| 18.9.2           | TRCSR Register                                                                                                              | 247 |

| 18.9.3           | TRCCR1 Register                                                                                                             | 247 |

| 18.9.4           | Count Source Switching                                                                                                      | 247 |

| 18.9.5           | Input Capture Function                                                                                                      | 248 |

| 18.9.6           | TRCMR Register in PWM2 Mode                                                                                                 | 248 |

| 18.9.7           | Count Source fOCO40M                                                                                                        | 248 |

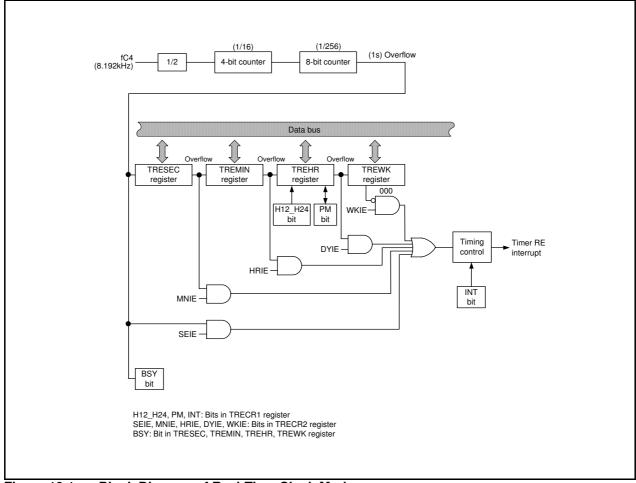

| 19. Time         | er RE                                                                                                                       | 249 |

|                  |                                                                                                                             |     |

|                  | Overview                                                                                                                    |     |

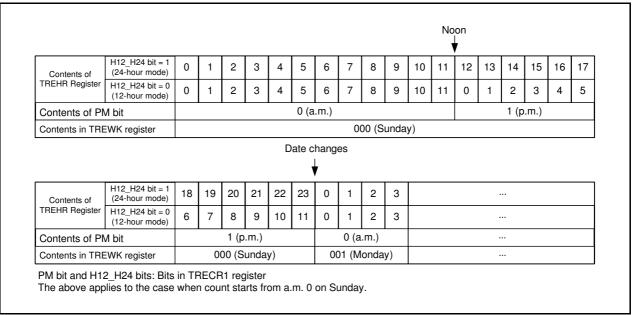

|                  | Real-Time Clock Mode                                                                                                        |     |

| 19.2.1           | Timer RE Second Data Register (TRESEC) in Real-Time Clock Mode                                                              |     |

| 19.2.2<br>19.2.3 | Timer RE Minute Data Register (TREMIN) in Real-Time Clock Mode  Timer RE Hour Data Register (TREHR) in Real-Time Clock Mode |     |

| 19.2.3           |                                                                                                                             |     |

| 19.2.4           | Timer RE Day of Week Data Register (TREWK) in Real-Time Clock Mode                                                          |     |

| 19.2.5           | Timer RE Control Register 2 (TRECR2) in Real-Time Clock Mode                                                                |     |

| 19.2.7           | Timer RE Count Source Select Register (TRECSR) in Real-Time Clock Mode                                                      |     |

| 19.4.1           | Times RL Count Source Select Register (TRECSR) in Real-Time Clock Mode                                                      | 230 |

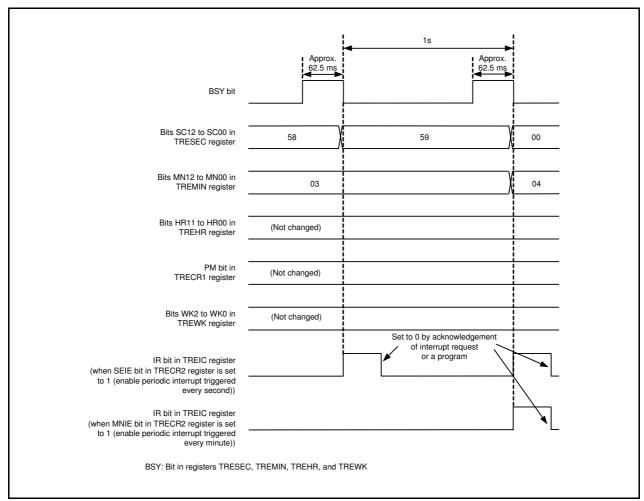

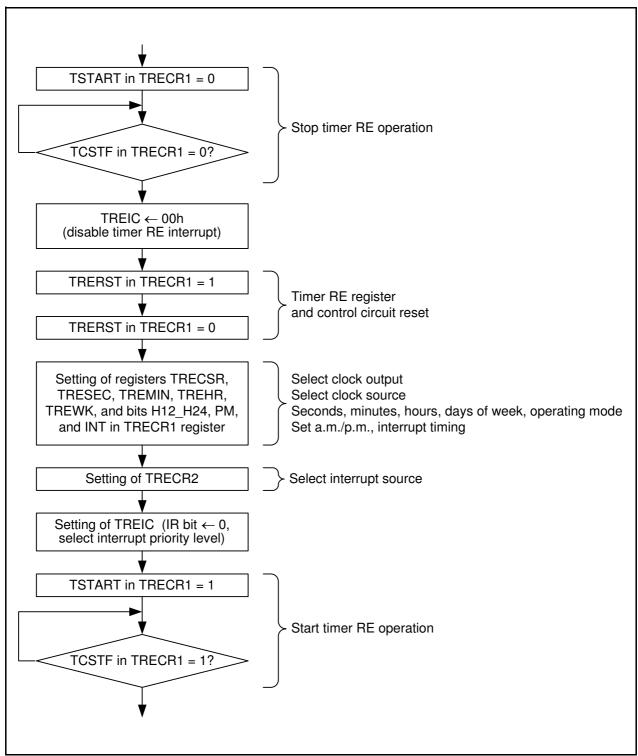

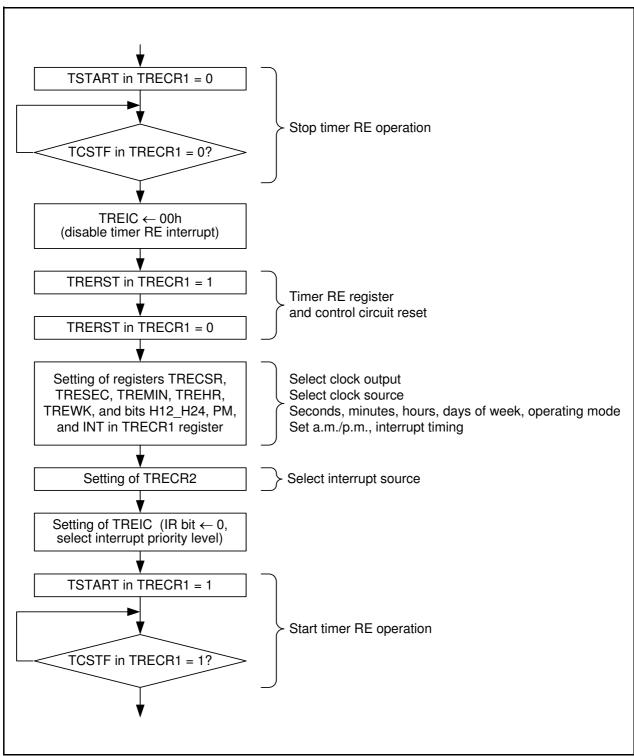

|   | 19.2.8                                                                                                                                                                                                     | Operating Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 237                                                                                                                                                 |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 19.3 N                                                                                                                                                                                                     | Votes on Timer RE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 258                                                                                                                                                 |

|   | 19.3.1                                                                                                                                                                                                     | Starting and Stopping Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 258                                                                                                                                                 |

|   | 19.3.2                                                                                                                                                                                                     | Register Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 258                                                                                                                                                 |

|   | 19.3.3                                                                                                                                                                                                     | Time Reading Procedure of Real-Time Clock Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 260                                                                                                                                                 |

|   |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                       |

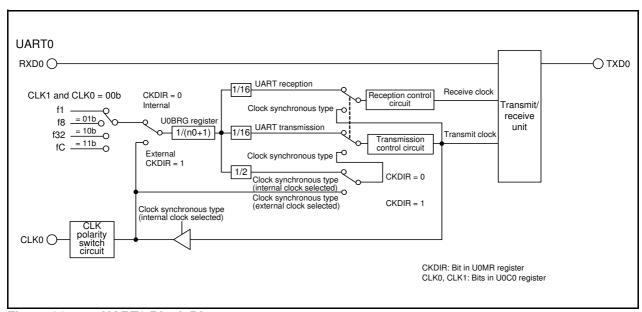

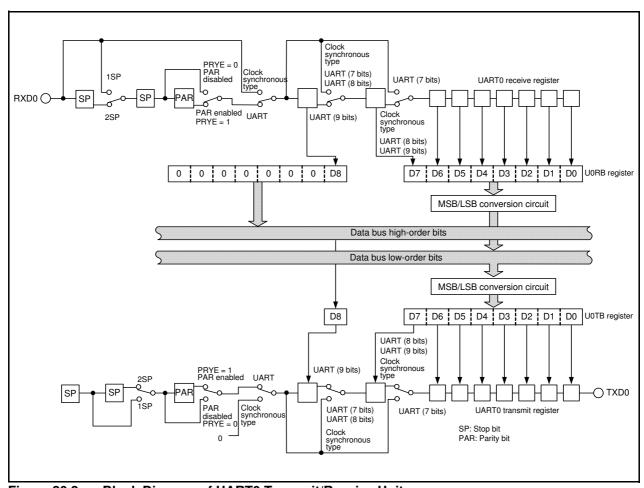

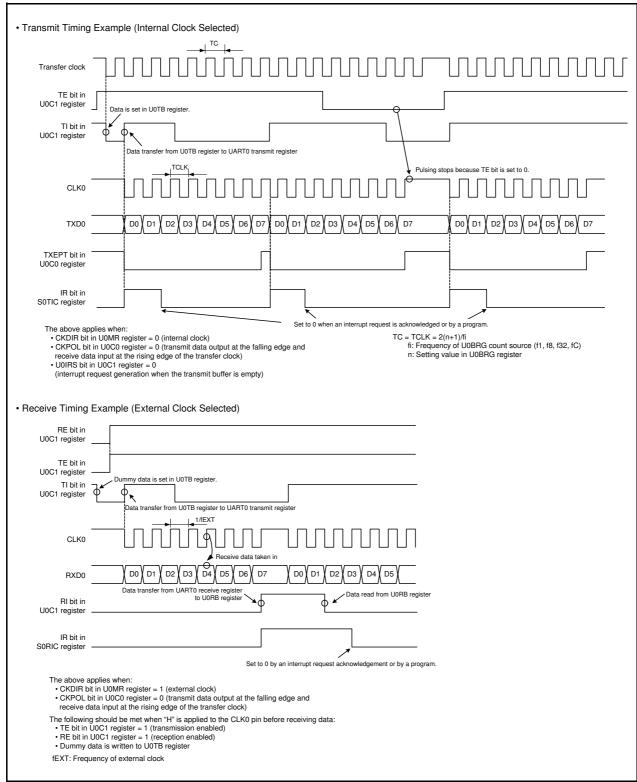

| 2 | 0. Seria                                                                                                                                                                                                   | I Interface (UART0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 261                                                                                                                                                   |

|   | 20.1 C                                                                                                                                                                                                     | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 261                                                                                                                                                 |

|   | 20.2 R                                                                                                                                                                                                     | legisters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                       |

|   | 20.2.1                                                                                                                                                                                                     | UART0 Transmit/Receive Mode Register (U0MR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                       |

|   | 20.2.2                                                                                                                                                                                                     | UART0 Bit Rate Register (U0BRG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                       |

|   | 20.2.3                                                                                                                                                                                                     | UART0 Transmit Buffer Register (U0TB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                       |

|   | 20.2.4                                                                                                                                                                                                     | UART0 Transmit/Receive Control Register 0 (U0C0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                       |

|   | 20.2.5                                                                                                                                                                                                     | UART0 Transmit/Receive Control Register 1 (U0C1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                       |

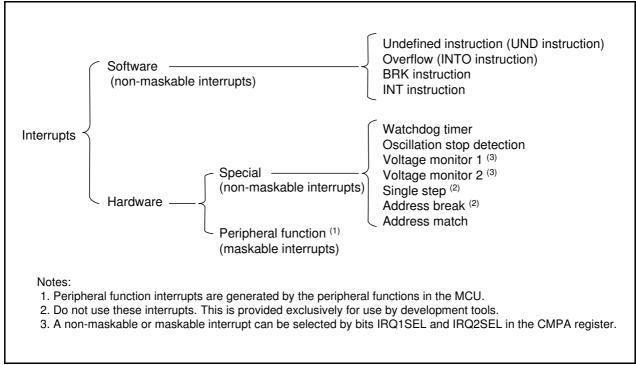

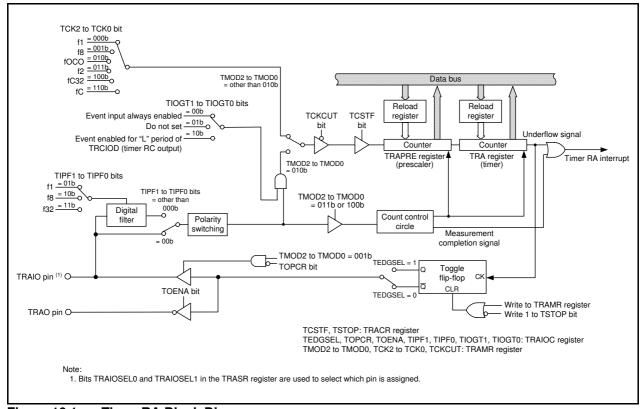

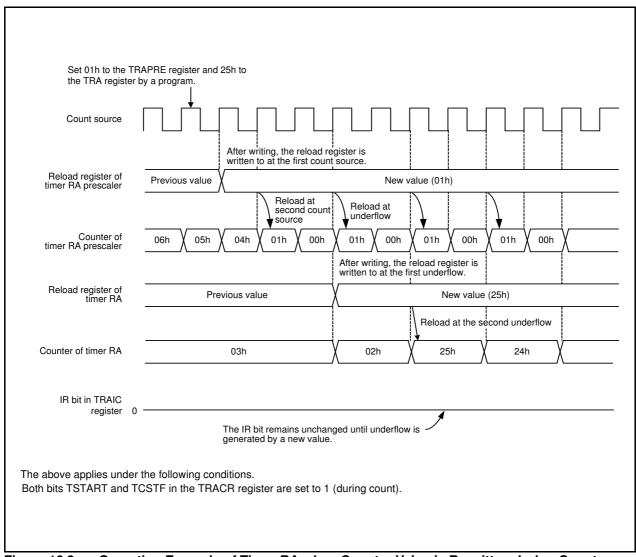

|   | 20.2.6                                                                                                                                                                                                     | UART0 Receive Buffer Register (U0RB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                       |